SFF Committee documentation may be purchased in electronic form. SFF specifications are available at ftp://ftp.seagate.com/sff

SFF Committee

#### SFF-8449

#### Specification for

### Shielded Cables Management Interface for SAS

Rev 2.0 September 18, 2013

Secretariat: SFF Committee

Abstract: This specification defines a common management interface for shielded cable assemblies. Physical layer and mechanical details of the connector interface are outside the scope of this document.

This specification provides a common reference for systems manufacturers, system integrators, and suppliers. This is an internal working specification of the SFF Committee, an industry ad hoc group.

This specification is made available for public review, and written comments are solicited from readers. Comments received by the members will be considered for inclusion in future revisions of this specification.

Support: This specification is supported by the identified member companies of the SFF Committee.

POINTS OF CONTACT:

Barry OlawskyI. Dal AllanHewlett PackardChairman SFF Committee11445 Compaq Center Drive West14426 Black Walnut CourtHouston, TX 77070Saratoga CA 95070Ph:281-514-8624Ph: 408-867-6630barry.olawsky@hp.comendlcom@acm.org

# EXPRESSION OF SUPPORT BY MANUFACTURERS

The following member companies of the SFF Committee voted in favor of this industry specification.

Amphenol Applied Micro Dell Computer EMC FCI Foxconn Hewlett Packard HGST IBM Lotes Tech LSI Molex NetApp Seagate Shenzhen TE Connectivity Volex

The following member companies of the SFF Committee voted to abstain on this industry specification.

Avago Emulex Finisar JDS Uniphase Luxshare-ICT Oclaro Panduit QLogic Sandisk Sumitomo Toshiba Western Digital Xyratex

The user's attention is called to the possibility that implementation to this Specification may require use of an invention covered by patent rights. By distribution of this specification, no position is taken with respect to the validity of a claim or claims or of any patent rights in connection therewith. Members of the SFF Committee which advise that a patent exists are required to provide a statement of willingness to grant a license under these rights on reasonable and non-discriminatory terms and conditions to applicants desiring to obtain such a license.

History: Rev 1.7 - Initial release Rev 1.8 - Table 5-2 editorial changes. Tables 5-2 and 5-9 changed due to recognition of industry practices. Rev 1.9 - Increased maximum Iman in Table 5-2 from 8mA to 30mA to enable use of a microcontroller instead of a segmented NVRAM. Rev 2.0 - Added industry document reference to SFF-8636 and SFF-8644

### Foreword

The development work on this specification was done by the SFF Committee, an industry group. The membership of the committee since its formation in August 1990 has included a mix of companies which are leaders across the industry.

When 2 1/2" diameter disk drives were introduced, there was no commonality on external dimensions e.g. physical size, mounting locations, connector type, and connector location, between vendors.

The first use of these disk drives was in specific applications such as laptop portable computers and system integrators worked individually with vendors to develop the packaging. The result was wide diversity, and incompatibility.

The problems faced by integrators, device suppliers, and component suppliers led to the formation of the SFF Committee as an industry ad hoc group to address the marketing and engineering considerations of the emerging new technology.

During the development of the form factor definitions, other activities were suggested because participants in the SFF Committee faced more problems than the physical form factors of disk drives. In November 1992, the charter was expanded to address any issues of general interest and concern to the storage industry. The SFF Committee became a forum for resolving industry issues that are either not addressed by the standards process or need an immediate solution.

Those companies which have agreed to support a specification are identified in the first pages of each SFF Specification. Industry consensus is not an essential requirement to publish an SFF Specification because it is recognized that in an emerging product area, there is room for more than one approach. By making the documentation on competing proposals available, an integrator can examine the alternatives available and select the product that is felt to be most suitable.

SFF Committee meetings are held during T10 weeks (see www.t10.org), and Specific Subject Working Groups are held at the convenience of the participants. Material presented at SFF Committee meetings becomes public domain, and there are no restrictions on the open mailing of material presented at committee meetings.

Most of the specifications developed by the SFF Committee have either been incorporated into standards or adopted as standards by EIA (Electronic Industries Association), ANSI (American National Standards Institute) and IEC (International Electrotechnical Commission).

If you are interested in participating or wish to follow the activities of the SFF Committee, the signup for membership and/or documentation can be found at:

### www.sffcommittee.com/ie/join.html

The complete list of SFF Specifications which have been completed or are currently being worked on by the SFF Committee can be found at:

# ftp://ftp.seagate.com/sff/SFF-8000.TXT

If you wish to know more about the SFF Committee, the principles which guide the activities can be found at:

ftp://ftp.seagate.com/sff/SFF-8032.TXT

Suggestions for improvement of this specification will be welcome. They should be sent to the SFF Committee, 14426 Black Walnut Ct, Saratoga, CA 95070.

| 1 | Scope                                                | 5                          |

|---|------------------------------------------------------|----------------------------|

| 2 | References                                           | 5                          |

|   | 2.1 Industry Documents                               | 5<br>5<br>5<br>5<br>5<br>6 |

|   | 2.2 SFF Specifications                               | 5                          |

|   | 2.3 Sources                                          | 5                          |

|   | 2.4 Conventions                                      | 6                          |

| 3 | Definitions                                          | б                          |

|   | 3.1 Fixed versus Free                                | б                          |

|   | 3.1.1 Fixed                                          | 6                          |

|   | 3.1.2 Free                                           | 6                          |

|   | 3.2 Passive Cable                                    | 6                          |

|   | 3.3 Active Cable                                     | 6                          |

| 4 | General Description                                  | 6                          |

|   | 4.1 Fixed-to-Free Side Block Diagram                 | 6                          |

|   | 4.2 Physical Cable Assembly Implementation           | 7                          |

|   | 4.2.1 Direct Attach                                  | 7                          |

|   | 4.2.2 Management Interface Scope                     | 8<br>9<br>9<br>9           |

| 5 | High Density (HD) Connector Physical Layer Interface | 9                          |

|   | 5.1 Signal Assignment                                | 9                          |

|   | 5.2 High Speed Serial Interface                      | 9                          |

|   | 5.3 Management Interface                             | 9                          |

|   | 5.3.1 Signal Definition                              | 10                         |

|   | 5.3.1.1 Vman                                         | 10                         |

|   | 5.3.1.2 Vact                                         | 10                         |

|   | 5.3.1.3 ModPrsL                                      | 10                         |

|   | 5.3.1.4 IntL                                         | 10                         |

|   | 5.3.1.5 SCL                                          | 10                         |

|   | 5.3.1.6 SDA                                          | 10                         |

|   | 5.3.2 Free Side Device Addressing                    | 10                         |

|   | 5.3.3 DC Electrical Characteristics                  | 11                         |

|   | 5.3.4 AC Electrical Characteristics                  | 11                         |

|   | 5.3.5 Absolute Maximum/Minimum Ratings               | 12                         |

|   | 5.4 Timing Requirements                              | 12                         |

|   | 5.5 Power Consumption Modes                          | 14                         |

|   | 5.6 Power Supply Filtering Network                   | 15                         |

|   | 5.7 Squelch (Active Cable Implementations)           | 16                         |

# FIGURES

| Figure 1-1 | Hierarchy of Interface Specifications (Example)       | 5  |

|------------|-------------------------------------------------------|----|

| Figure 4-1 | External Cable Management Interface Block Diagram     | 7  |

| Figure 4-2 | Direct Attach Cable Assembly Implementation           | 8  |

| Figure 4-3 | Management Interface Scope                            | 8  |

| Figure 5-1 | Inrush Current (Vact pins)                            | 12 |

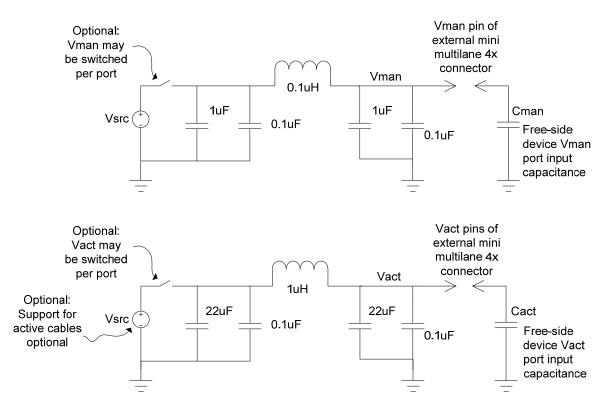

| Figure 5-2 | Recommended Fixed Side Power Supply Filtering Network | 16 |

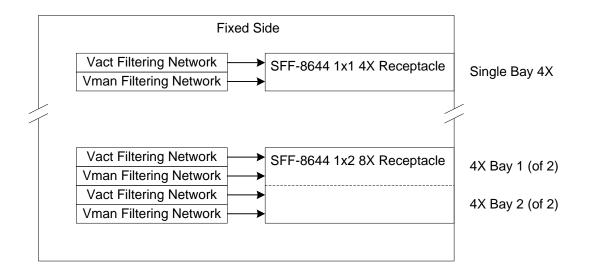

| Figure 5-3 | Filtering Networks with Multi-Bay Receptacle Designs  | 16 |

# TABLES

|           | IADIED                                       |    |

|-----------|----------------------------------------------|----|

| Table 5-1 | HD Connector Physical Layer Interface        | 9  |

| Table 5-2 | DC Electrical Characteristics                | 11 |

| Table 5-3 | AC Electrical Characteristics                | 11 |

| Table 5-4 | Absolute Maximum/Minimum Ratings             | 12 |

| Table 5-5 | Timing for soft control and status functions | 13 |

| Table 5-6 | Disable Control Timing                       | 14 |

| Table 5-7 | Power Consumption Control Functionality      | 14 |

|           | Reduced Power Consumption Levels             | 15 |

| Table 5-9 | Minimum Operating Voltage                    | 15 |

|           |                                              |    |

SFF Committee --

### Common Management Interface

#### 1 Scope

This specification defines a management interface for SFF-8644 external cable assembly implementations. The detailed mechanical design is documented in SFF-8644. The interface memory map and protocol operation are also outside the scope of this specification but can be found in SFF-8636. This document provides a detailed description of the electrical interface characteristics.

This approach facilitates a common memory map and management interface for applications with different mechanical, physical layer and otherwise different implementations. For example, SFF-8449 defines a four channel solution which documents the management interface physical layer, references SFF-8636 to ensure compatibility with the common memory map and protocol. See figure 1-1.

| SFF-8644               | SFF-8636            |

|------------------------|---------------------|

| Mechanical Details and | Common Memory Map   |

| Pin Identification     | Protocol and Timing |

### FIGURE 1-1 HIERARCHY OF INTERFACE SPECIFICATIONS (EXAMPLE)

Note that the SFF-8636 memory map is shared amongst multiple standards. SFF-8636 may include signals beyond the scope of the SFF-8449 interface.

### 2 References

The SFF Committee activities support the requirements of the storage industry, and it is involved with several standards.

#### 2.1 Industry Documents

The following interface standards and specifications are relevant to this specification.

SFF-8636 Common Management Interface SFF-8644 Mini Multilane 12 Gbs 8/4X Shielded Connector

### 2.2 SFF Specifications

There are several projects active within the SFF Committee. The complete list of specifications which have been completed or are still being worked on are listed in the specification at  $\frac{ftp://ftp.seagate.com/sff/SFF-8000.TXT}{ftp://ftp.seagate.com/sff/SFF-8000.TXT}$

### 2.3 Sources

Those who join the SFF Committee as an Observer or Member receive electronic copies of the minutes and SFF specifications (<u>http://www.sffcommittee.com/ie/join.html</u>).

Copies of ANSI standards may be purchased from the Inter-National Committee for

Information Technology Standards (http://tinyurl.com/c4psg).

### 2.4 Conventions

The American convention of numbering is used (i.e., a comma separates the thousands and higher multiples, and a period is used as the decimal point). This is equivalent to the ISO/IEC convention of a space and comma.

| American    | French      | ISO         |

|-------------|-------------|-------------|

| 0.6         | 0,6         | 0.6         |

| 1,000       | 1 000       | 1 000       |

| 1,323,462.9 | 1 323 462,9 | 1 323 462.9 |

### 3 Definitions

### 3.1 Fixed versus Free

## 3.1.1 Fixed

The terminology "fixed" is used to describe the gender of the mating side of the connector that accepts its mate upon mating. This gender is frequently, but not always, associated with the common terminology "receptacle". Other terms commonly used are "female" and "socket connector". The term "fixed" is adopted from EIA standard terminology as the gender that most commonly exists on the fixed end of a connection, for example, on the board or bulkhead side.

## 3.1.2 Free

The terminology "free" is used to describe the gender of the mating side of the connector that penetrates its mate upon mating. This gender is frequently, but not always, associated with the common terminology "plug". Other terms commonly used are "male" and "pin connector". The term "free" is adopted from EIA standard terminology as the gender that most commonly exists on the free end of a connection, for example, on the cable side.

### 3.2 Passive Cable

In this standard, a passive cable only requires power to operate the management interface circuitry.

### 3.3 Active Cable

In this standard, an active cable requires power for circuitry that is integral to any of the TX/RX high speed serial channels supported by the cable. In addition, the active cable requires power to operate the management interface.

### 4 General Description

The external cable management interface provides a method for the fixed side to determine the characteristics and status of the free side. In some implementations, the interface also provides a mechanism to control the operation of the free side circuitry. For the case where the free side is a cable, the fixed side can determine if the cable is passive, active copper, or active optical. Parameters such as supplier, part number, propagation delay and loss (for passive cables) can also be determined.

### 4.1 Fixed-to-Free Side Block Diagram

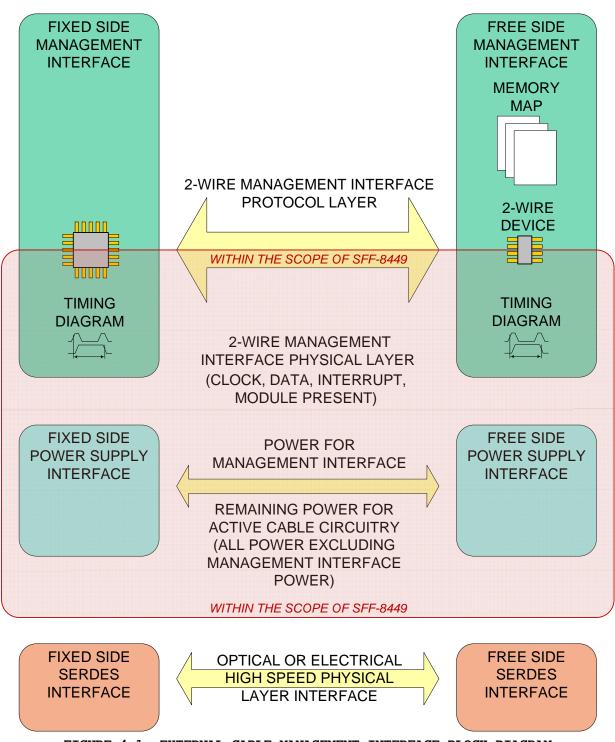

Figure 4-1 depicts the fixed-to-free side management interface. Note the limitations in scope of SFF-8449.

FIGURE 4-1 EXTERNAL CABLE MANAGEMENT INTERFACE BLOCK DIAGRAM

# 4.2 Physical Cable Assembly Implementation

# 4.2.1 Direct Attach

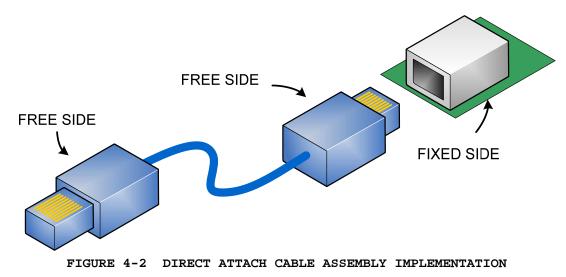

Figure 4-2 depicts a direct attach passive, active copper or optical cable interconnect implementation.

# 4.2.2 Management Interface Scope

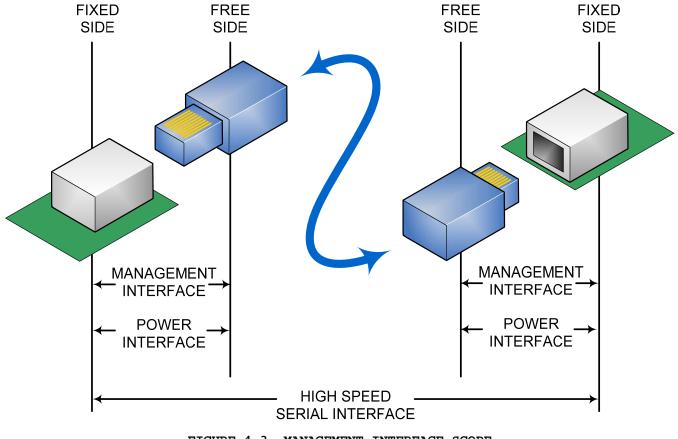

Figure 4-3 depicts the limited scope of the management and active cable power interfaces. Note that management and power interfaces do not extend from one free side end of the cable to the other.

FIGURE 4-3 MANAGEMENT INTERFACE SCOPE

### 5 High Density (HD) Connector Physical Layer Interface

## 5.1 Signal Assignment

The fixed and free-side HD connector interface supports four bi-directional high speed differential serial links and a management interface. Table 5-1 identifies all signals of the connector interface.

| Signal   | Pin | Mating | Definition                                            |

|----------|-----|--------|-------------------------------------------------------|

|          |     | Level  |                                                       |

| Reserved | A1  | Second | Reserved for future use                               |

| IntL     | A2  | Second | Management interface interrupt signal                 |

| GND      | A3  | First  | Signal ground                                         |

| RX1+     | A4  | Third  | Fixed side receiver channel 1 non-inverting input     |

| RX1-     | A5  | Third  | Fixed side receiver channel 1 inverting input         |

| GND      | A6  | First  | Signal ground                                         |

| RX3+     | A7  | Third  | Fixed side receiver channel 3 non-inverting input     |

| RX3 -    | A8  | Third  | Fixed side receiver channel 3 inverting input         |

| GND      | A9  | First  | Signal ground                                         |

| Vact     | B1  | Second | Free side power input for non-management interface    |

|          |     |        | circuitry                                             |

| ModPrsL  | B2  | Second | Free side active low present output                   |

| GND      | B3  | First  | Signal ground                                         |

| RX0+     | B4  | Third  | Fixed side receiver channel 0 non-inverting input     |

| RX0 -    | B5  | Third  | Fixed side receiver channel 0 inverting input         |

| GND      | B6  | First  | Signal ground                                         |

| RX2+     | B7  | Third  | Fixed side receiver channel 2 non-inverting input     |

| RX2-     | B8  | Third  | Fixed side receiver channel 2 inverting input         |

| GND      | B9  | First  | Signal ground                                         |

| SCL      | C1  | Second | Management interface serial clock                     |

| SDA      | C2  | Second | Management interface serial data output               |

| GND      | C3  | First  | Signal ground                                         |

| TX1+     | C4  | Third  | Fixed side transmitter channel 1 non-inverting output |

| TX1-     | C5  | Third  | Fixed side transmitter channel 1 inverting output     |

| GND      | C6  | First  | Signal ground                                         |

| TX3+     | C7  | Third  | Fixed side transmitter channel 3 non-inverting output |

| TX3 -    | C8  | Third  | Fixed side transmitter channel 3 inverting output     |

| GND      | C9  | First  | Signal ground                                         |

| Vact     | D1  | Second | Free side power input for non-management interface    |

|          |     |        | circuitry                                             |

| Vman     | D2  | Second | Free side power input for management interface        |

|          |     |        | circuitry                                             |

| GND      | D3  | First  | Signal ground                                         |

| TX0+     | D4  | Third  | Fixed side transmitter channel 0 non-inverting output |

| TX0-     | D5  | Third  | Fixed side transmitter channel 0 inverting output     |

| GND      | D6  | First  | Signal ground                                         |

| TX2+     | D7  | Third  | Fixed side transmitter channel 2 non-inverting output |

| TX2-     | D8  | Third  | Fixed side transmitter channel 2 inverting output     |

| GND      | D9  | First  | Signal ground                                         |

TABLE 5-1 HD CONNECTOR PHYSICAL LAYER INTERFACE

## 5.2 High Speed Serial Interface

Electrical characteristics of signals on pins A4, A5, A7, A8, B4, B5, B7, B8, C4, C5, C7, C8, D4, D5, D7 and D8 are outside the scope of this document.

## 5.3 Management Interface

Pins A1, A2, B1, B2, C1, C2, D1 and D2 comprise the management interface. Note that GND pins A3, A6, A9, B3, B6, B9, C3, C6, C9, D3, D6 and D9 are required for reliable management interface operation although they are not classified as part of the management interface.

# 5.3.1 Signal Definition

#### 5.3.1.1 Vman

The fixed-side shall provide power for the free-side device management interface circuitry on the Vman signal. Removal of power from the Vman signal shall disable the free-side management circuitry. Upon restoration of power to the Vman signal, the management interface shall perform all necessary power up tasks. The SFF-8449 management interface does not include a dedicated reset signal. To reset the free-side management interface circuitry, the fixed side may cycle power off and on. See table 5-5 for Initialization Time requirements, signal levels and other reset circuitry parameters.

### 5.3.1.2 Vact

To support active cable designs, the fixed side shall provide power to both Vact pins in addition to the Vman pin. See section 5.4 for electrical requirements. All Vact pins shall be not connected on passive free side designs. Since Vman provides reset functionality for the management interface, no power sequencing requirements for Vman with respect to Vact shall be placed on the fixed side other than those specified in section 5.5.

### 5.3.1.3 ModPrsL

The fixed-side shall de-assert the active-low ModPrsL signal. When mated with the fixed side, the free-side device shall assert ModPrsL low. During power up initialization, the free-side device shall assert ModPrsL prior to assertion of IntL. ModPrsL shall remain asserted until the free-side device is no longer mated to the fixed side. See section 5.4 for electrical characteristics of the signal, fixed-side and free-side termination characteristics.

## 5.3.1.4 IntL

The fixed-side shall de-assert the active-low IntL signal. The free-side device shall assert IntL low to indicate that an event has occurred that requires interrupt service. The free-side device shall de-assert IntL after the fixed side has cleared the appropriate interrupt flag bits within the free-side device memory map. In addition, the free-side device indicates completion of reset, including power up initialization by asserting the IntL signal with the Data\_Not\_Ready (See SFF-8636) bit negated. IntL can be cleared as detailed in SFF-8636. See section 5.4 for electrical characteristics of the signal, fixed-side and free-side termination characteristics. Timing requirements are specified in section 5.5.

### 5.3.1.5 SCL

Two-wire interface clock.

### 5.3.1.6 SDA

Two-wire interface data.

## 5.3.2 Free Side Device Addressing

The SFF-8449 management interface does not provide a mechanism to address individual free-side devices. The fixed-side shall provide an independent physical layer interface for each free-side device. Multiple free-side devices shall not share the same clock and data signals.

Electrical Characteristics

| 5.3.3 DC Electrical Characteristics |

|-------------------------------------|

|-------------------------------------|

| Signal                                                           | Symbol   | Min         | Max         | Unit    | Condition               |  |  |  |  |

|------------------------------------------------------------------|----------|-------------|-------------|---------|-------------------------|--|--|--|--|

|                                                                  | Vol      | 0           | 0.4         | V       | Iol=3.0mA               |  |  |  |  |

| SCL, SDA                                                         | Voh      | Vman-0.5    | Vman+0.3    | V       |                         |  |  |  |  |

|                                                                  | Vil      | -0.3        | Vman*0.3    | V       |                         |  |  |  |  |

| (see note 1)                                                     | Vih      | Vman*0.7    | Vman+0.5    | V       |                         |  |  |  |  |

|                                                                  | Vol      | 0           | 0.4         | V       | Iol=2.0mA               |  |  |  |  |

| ModPrsL, IntL                                                    | Voh      | Vman-0.5    | Vman+0.3    | V       |                         |  |  |  |  |

|                                                                  | Vil      | -0.3        | Vman*0.3    | V       |                         |  |  |  |  |

| (see note 2)                                                     | Vih      | Vman*0.7    | Vman+0.5    | V       |                         |  |  |  |  |

| Management Interface                                             |          |             |             |         |                         |  |  |  |  |

| Power Supply Voltage                                             | Vman     | 3.0         | 3.6         | V       |                         |  |  |  |  |

| Management Interface                                             |          |             |             |         |                         |  |  |  |  |

| Power Supply Current                                             | Iman     | -           | 30          | mA      |                         |  |  |  |  |

| Active Circuitry Power                                           |          |             |             |         | See section 5.6 for     |  |  |  |  |

| Supply Voltage                                                   | Vact     | -           | 3.6         | V       | reduced voltage support |  |  |  |  |

| Note 1. Fixed side termi                                         |          |             |             |         |                         |  |  |  |  |

| capacitance and the inpu                                         | t rise t | ime (outsid | le the scop | pe of t | this document).         |  |  |  |  |

| Note 2. 10KOhm maximum fixed side termination impedance to Vman. |          |             |             |         |                         |  |  |  |  |

| TABLE 5-2 | DC | ELECTRICAL | CHARACTERISTICS    |

|-----------|----|------------|--------------------|

|           | 20 |            | CIMMUICI MICEDITCD |

# 5.3.4 AC Electrical Characteristics

| Signal                                                                | Max      | Unit    | Condition                                                                                                         |  |  |  |  |

|-----------------------------------------------------------------------|----------|---------|-------------------------------------------------------------------------------------------------------------------|--|--|--|--|

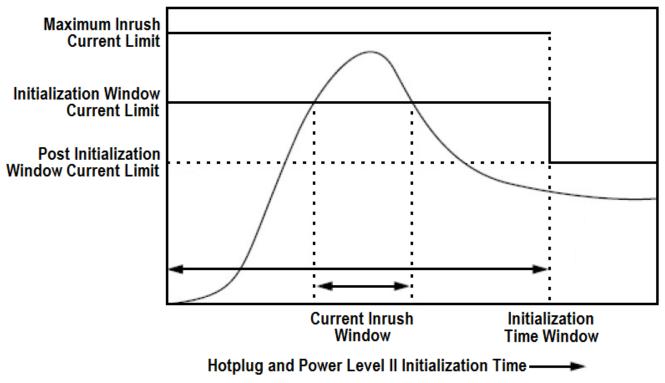

| Initialization Time Window                                            | 500      | ms      |                                                                                                                   |  |  |  |  |

| Current Inrush Window Duration                                        | 150      | us      |                                                                                                                   |  |  |  |  |

| Power Supply Noise including ripple                                   | 50       | mV      | 1kHz to frequency of operation measured at Vcc host.                                                              |  |  |  |  |

|                                                                       |          |         |                                                                                                                   |  |  |  |  |

| Current Inrush Limit with<br>LPMode enabled                           | 600      | mA      | Occurs within initialization<br>time window. Pulse width less<br>than 50 micro-seconds.                           |  |  |  |  |

| Sustained Initialization Time<br>Current Limit with LPMode<br>enabled | 500      | mA      | Maximum current within<br>initialization time window<br>excluding 50 micro-second<br>current inrush pulse window. |  |  |  |  |

| Current Inrush Limit with<br>LPMode disabled                          | 2500     | mA      | Occurs within initialization<br>time window. Pulse width less<br>than 50 micro-seconds.                           |  |  |  |  |

| Sustained initialization time<br>current with LPMode disabled         | 750      | mA      | Maximum current within<br>initialization time window<br>excluding 50 micro-second<br>current inrush pulse window. |  |  |  |  |

|                                                                       |          |         |                                                                                                                   |  |  |  |  |

| Note the Post Initialization Win                                      | ndow Cur | rent Li | mit is described in section 5.6.                                                                                  |  |  |  |  |

# TABLE 5-3 AC ELECTRICAL CHARACTERISTICS

FIGURE 5-1 INRUSH CURRENT (VACT PINS)

# 5.3.5 Absolute Maximum/Minimum Ratings

| Signal                                                                                                       | Min  | Max      | Unit | Condition                                                                                                |  |  |

|--------------------------------------------------------------------------------------------------------------|------|----------|------|----------------------------------------------------------------------------------------------------------|--|--|

| Vman                                                                                                         | -0.3 | 3.6      | V    |                                                                                                          |  |  |

| Vact                                                                                                         | -0.3 | 3.6      | V    |                                                                                                          |  |  |

| SCL, SDA, ModPrsL, IntL                                                                                      | -0.3 | Vman+1.0 | V    | With respect to GND                                                                                      |  |  |

| Free-side device Vact<br>input capacitance                                                                   | -    | 22       | uF   | Both pins combined. This<br>value includes all<br>variations due to process,<br>voltage and temperature. |  |  |

| Free-side device Vman<br>input capacitance                                                                   | -    | 1        | uF   | This value includes all<br>variations due to process,<br>voltage and temperature.                        |  |  |

| Free-side device input<br>capacitance for SCL and<br>SDA                                                     | -    | 14       | pF   |                                                                                                          |  |  |

| Note the differential high speed serial receiver input voltage rating is outside the scope of this document. |      |          |      |                                                                                                          |  |  |

# TABLE 5-4 ABSOLUTE MAXIMUM/MINIMUM RATINGS

# 5.4 Timing Requirements

The free side device software control and status function timing specifications are described in Table 5-5.

| TABLE 5-5 TIM | AING FOR | SOFT | CONTROL | AND | STATUS | FUNCTIONS |

|---------------|----------|------|---------|-----|--------|-----------|

|---------------|----------|------|---------|-----|--------|-----------|

| Parameter                                                                             | Symbol        | Max    | Unit   | Conditions                                                                     |  |  |

|---------------------------------------------------------------------------------------|---------------|--------|--------|--------------------------------------------------------------------------------|--|--|

| Free Side                                                                             | t init        | 2000   | ms     | Time from power on <sup>2</sup> or hot plug event                              |  |  |

| Active Device                                                                         |               | 2000   | iiis   | until the free side active device is                                           |  |  |

| Initialization                                                                        |               |        |        | fully functional <sup>3</sup> . Does not include                               |  |  |

| Time                                                                                  |               |        |        | delay due to device interrogation.                                             |  |  |

| Management                                                                            | t man init    | 2000   | ms     | Time from application of Vman or hot                                           |  |  |

| Interface                                                                             |               | 2000   | ino    | plug event until the free side device                                          |  |  |

| Initialization                                                                        |               |        |        | management interface is fully                                                  |  |  |

| Time                                                                                  |               |        |        | functional. This requirement applies to                                        |  |  |

| 11110                                                                                 |               |        |        | both passive and active free side                                              |  |  |

|                                                                                       |               |        |        | designs.                                                                       |  |  |

| Serial Bus                                                                            | t serial      | 2000   | ms     | Time from power on <sup>2</sup> until the free side                            |  |  |

| Hardware Ready                                                                        |               |        |        | responds to data transmission over the                                         |  |  |

| Time                                                                                  |               |        |        | 2-wire serial bus                                                              |  |  |

| Monitor Data                                                                          | t data        | 2000   | ms     | Time from power on <sup>2</sup> to data not ready,                             |  |  |

| Ready Time                                                                            |               |        |        | IntL asserted and bit 0 of Byte 2,                                             |  |  |

| 2                                                                                     |               |        |        | deasserted. See SFF-8636.                                                      |  |  |

| LPMode Assert                                                                         | ton LPMode    | 100    | us     | Delay from low power mode enable until                                         |  |  |

| Time                                                                                  | _             |        |        | the free side device power consumption                                         |  |  |

|                                                                                       |               |        |        | does not exceed Power Level 1. See                                             |  |  |

|                                                                                       |               |        |        | SFF-8636.                                                                      |  |  |

| IntL Assert                                                                           | ton IntL      | 200    | ms     | Time from occurrence of condition                                              |  |  |

| Time                                                                                  | _             |        |        | triggering IntL until Vout:IntL=Vol                                            |  |  |

| IntL Deassert                                                                         | toff IntL     | 500    | us     | Time from clear on read <sup>4</sup> operation of                              |  |  |

| Time                                                                                  | _             |        |        | associated flag until Vout:IntL=Voh.                                           |  |  |

|                                                                                       |               |        |        | This includes deassert times for Rx                                            |  |  |

|                                                                                       |               |        |        | LOS, Tx Fault and other flag bits. See                                         |  |  |

|                                                                                       |               |        |        | SFF-8636.                                                                      |  |  |

| Rx LOS Assert                                                                         | ton_los       | 100    | ms     | Time from Rx LOS state to Rx LOS bit                                           |  |  |

| Time                                                                                  | _             |        |        | set (value = 1b) and IntL asserted.                                            |  |  |

|                                                                                       |               |        |        | See SFF-8636.                                                                  |  |  |

| Tx Fault Assert                                                                       | ton_Txfault   | 200    | ms     | Time from Tx Fault state to Tx Fault                                           |  |  |

| Time                                                                                  |               |        |        | bit set (value = 1b) and IntL                                                  |  |  |

|                                                                                       |               |        |        | asserted. See SFF-8636.                                                        |  |  |

| Flag Assert                                                                           | ton_flag      | 200    | ms     | Time from occurrence of condition                                              |  |  |

| Time                                                                                  |               |        |        | triggering flag to associated flag bit                                         |  |  |

|                                                                                       |               |        |        | set (value = 1b) and IntL asserted.                                            |  |  |

|                                                                                       |               |        |        | See SFF-8636.                                                                  |  |  |

| Mask Assert                                                                           | ton_mask      | 100    | ms     | Time from mask bit set $(value = 1b)^{1}$                                      |  |  |

| Time                                                                                  |               |        |        | until associated IntL assertion is                                             |  |  |

|                                                                                       |               |        |        | inhibited . See SFF-8636.                                                      |  |  |

| Mask Deassert                                                                         | toff_mask     | 100    | ms     | Time from mask bit cleared (value =                                            |  |  |

| Time                                                                                  |               |        |        | 0b) <sup>1</sup> until associated IntL operation                               |  |  |

| Application                                                                           | t matagal     | 100    |        | resumes. See SFF-8636.                                                         |  |  |

| Application or<br>Rate Select                                                         | t_ratesel     | 100    | ms     | Time from change of state of Application or Rate Select bit <sup>1</sup> until |  |  |

| Change Time                                                                           |               |        |        | transmitter or receiver bandwidth is                                           |  |  |

| Change TTILE                                                                          |               |        |        | in conformance with appropriate                                                |  |  |

|                                                                                       |               |        |        | specification. See SFF-8636.                                                   |  |  |

| Power over-ride                                                                       | ton Pdown     | 100    | ms     | Time from P Down bit set $(value = 1b)^{1}$                                    |  |  |

| or Power-set                                                                          |               |        |        | until module power consumption reaches                                         |  |  |

| Assert Time                                                                           |               |        |        | Power Level 1. See SFF-8636.                                                   |  |  |

| Power over-ride                                                                       | toff Pdown    | 300    | ms     | Time from P Down bit cleared (value =                                          |  |  |

| or Power-set                                                                          |               |        |        | 0b) <sup>1</sup> until the module is fully                                     |  |  |

| Deassert Time                                                                         |               |        |        | functional <sup>3</sup> See SFF-8636.                                          |  |  |

|                                                                                       | ed from falli | ng clo | ck eda | e after stop bit of write transaction                                          |  |  |

|                                                                                       |               |        |        | n is defined as the instant when all                                           |  |  |

|                                                                                       |               |        |        |                                                                                |  |  |

| supply voltages reach and remain at or above the minimum level specified in Table 5-2 |               |        |        |                                                                                |  |  |

| Note 3. Fully functional is defined as IntL asserted due to data not ready            |               |        |        |                                                                                |  |  |

| bit, bit 0 byte 2, deasserted. The module should also meet optical and                |               |        |        |                                                                                |  |  |

| electrical specifications.                                                            |               |        |        |                                                                                |  |  |

|                                                                                       |               |        |        |                                                                                |  |  |

|                                                                                       |               |        |        |                                                                                |  |  |

|                                       | INDER D-0    | DIGRDI  |        | IKOH TIMING                                                                                                                          |

|---------------------------------------|--------------|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                             | Symbol       | Max     | Unit   | Conditions                                                                                                                           |

|                                       |              |         |        |                                                                                                                                      |

|                                       |              |         |        |                                                                                                                                      |

| Tx Disable<br>Assert Time             | ton_txdis    | 100     | ms     | Time from Tx Disable bit set<br>(value = 1b) <sup>1</sup> until optical output<br>falls below 10% of nominal. See<br>SFF-8636.       |

| Tx Disable<br>Deassert Time           | toff_txdis   | 400     | ms     | Time from Tx Disable bit cleared<br>(value = 0b) <sup>1</sup> until optical output<br>rises above 90% of nominal. See<br>SFF-8636.   |

| Rx Output<br>Disable Assert<br>Time   | ton_rxdis    | 100     | ms     | Time from Rx Output Disable bit<br>set (value = 1b) <sup>†</sup> until Rx output<br>falls below 10% of nominal. See<br>SFF-8636.     |

| Rx Output<br>Disable Deassert<br>Time | toff_rxdis   | 100     | ms     | Time from Rx Output Disable bit<br>cleared (value = 0b) <sup>1</sup> until Rx<br>output rises above 90% of nominal.<br>See SFF-8636. |

|                                       |              |         |        |                                                                                                                                      |

| Note 1: Measured                      | from falling | g cloci | k edge | after stop bit of write transaction                                                                                                  |

Timing requirements for TX and RX disable controls are defined in table 5-6.

| TABLE | 5-6 | DISABLE | CONTROL | TIMING |  |

|-------|-----|---------|---------|--------|--|

|-------|-----|---------|---------|--------|--|

### 5.5 Power Consumption Modes

The management interface provides a mechanism to limit free side device power consumption by the Vact power inputs.

If the Power Override read/write bit (See SFF-8636, page 00h, byte 93, bit 0) is low, then the free-side device power is in the low power mode and power consumption shall be 1.5W or less. If the Power Override bit is in the high state and the Power Set read/write bit (see SFF-8636, page 00h, byte 93, bit 1) is low, then the freeside device power consumption may be greater than 1.5W. For the latter case, the Extended Identifier read-only bits (see SFF-8636, page 00h, byte 129, bits 6-7) indicate the maximum consumption for the specific free-side device.

If the Extended Identifier bits indicate power consumption greater than 1.5W and the free side device is in low power mode, then the free side device shall reduce power consumption to 1.5W or less. The exact method of reducing power consumption is not specified. However, it is likely that either the Tx or Rx or both will not be operational in this state.

If both Extended Identifier bits are in the low state, then the free side device power consumption shall be 1.5W or less. In this case, the free side device shall be fully functional regardless of the power mode.

A truth table for the relevant configurations of the Power Override, Power Set and Extended Identifier bits is shown in table 5-7.

| Power    | Power | Byte 129, | Module Power Allowed |

|----------|-------|-----------|----------------------|

| Override | Set   | bits 7-6  |                      |

| 0        | Х     | Х         | Low Power (1.5W)     |

| 1        | 0     | 00        | High Power (1.5W)    |

| 1        | 0     | 01        | High Power (2.0W)    |

| 1        | 0     | 10        | High Power (2.5W)    |

| 1        | 0     | 11        | High Power (3.5W)    |

| TABLE 5-7 | POWER | CONSUMPTION | CONTROL | FUNCTIONALITY |

|-----------|-------|-------------|---------|---------------|

|-----------|-------|-------------|---------|---------------|

| 1         | 1        | Х       | L      | ow Power ( | 1.5W)     |

|-----------|----------|---------|--------|------------|-----------|

| Note: The | symbol ' | X' in a | column | indicates  | any entry |

| satisfies | the cond | ition.  |        |            |           |

The free side device may declare maximum power consumption levels less than 1.5W by using the using read-only 'Advanced Low Power Mode' parameter shown in table 5-8. For example, if the fixed side does not support free side devices consuming more than 1W, this parameter will allow the fixed side to determine if it has adequate power allocated prior to application of power to the Vact pins. All states not listed in table 5-8 are reserved.

TABLE 5-8 REDUCED POWER CONSUMPTION LEVELS

| Advanced Low Power Mode<br>(Byte 110, bits 7-4) | Declared Maximum Power Consumption    |

|-------------------------------------------------|---------------------------------------|

| 0000                                            | Advanced Low Power Mode Not supported |

| 0001                                            | 1W                                    |

| 0010                                            | 0.75W                                 |

| 0011                                            | 0.5W                                  |

| Note: Free-side power lev<br>Vact inputs.       | rels specified for 3.3V level on both |

Additional power savings can be obtained by reducing the Vact input voltage level. The read only minimum operating voltage parameter is specified by bits 2-0 of byte 110. All states not listed in table 5-9 are reserved.

| Minimum Operating Voltage<br>(Byte 110, bits 2-0) | Declared Minimum Operating Voltage                        |

|---------------------------------------------------|-----------------------------------------------------------|

| 000                                               | Not Supported (Default is nominal 3.3V). See section 5,4. |

| 001                                               | 2.3V                                                      |

| 010                                               | 1.7V                                                      |

| 011                                               | Reserved                                                  |

TABLE 5-9 MINIMUM OPERATING VOLTAGE

# 5.6 Power Supply Filtering Network

The following fixed side power supply filtering network is recommended for the Vman and Vact output pins. The network isolates the fixed side Vsrc power rail from transients induced on the Vact and Vman power rails during hotplug events.

FIGURE 5-2 RECOMMENDED FIXED SIDE POWER SUPPLY FILTERING NETWORK

For proper operation of the filtering networks with multi-bay receptacles, one instance of both networks (Vman and Vact) is required for each 4X mini multilane bay. See figure 5-3.

### 5.7 Squelch (Active Cable Implementations)

SFF-8449 compliant cable assemblies are non-separable. Functionality of circuitry within the active cable assembly integral to the TX/RX channel such as squelch control is outside the scope of this standard.