SFF Committee documentation may be purchased in hard copy or electronic form. SFF specifications are available at ftp://ftp.seagate.com/sff

SFF Committee

#### SFF-8429 Specification for

#### Signal Specification Architecture for HSS Links

Rev 1.1 June 27, 2005

Secretariat: SFF Committee

Abstract: This specification defines the architectural requirements for specifying the performance of the signals and signal tolerance in links where the components are intended to be interoperable and interchangeable. This subject is important to most enclosure to enclosure and intra-building wiring applications. Specifically the following transport technologies may be affected: Fibre Channel, Ethernet, Infiniband, SAS, and others. Other applications such as power and telecom for these general-purpose considerations are also possible.

This specification provides a common specification for systems manufacturers, system integrators, and suppliers of interconnect components. This is an internal working specification of the SFF Committee, an industry ad hoc group.

This specification is made available for public review, and written comments are solicited from readers. Comments received by the members will be considered for inclusion in future revisions of this specification.

The description of a methodology in this specification does not assure that the methodology is actually used in published or draft standards. Methodologies must comply with this specification to achieve interoperability and interchangeablity between suppliers of link components.

Support: This specification is supported by the identified member companies of the SFF Committee.

POINTS OF CONTACT:

Bill Ham Hewlett Packard 165 Dascomb Road Andover, MA 01810 978 828-9102 Bill.Ham@HP.com I. Dal Allan Chairman SFF Committee 14426 Black Walnut Court Saratoga CA 95070 408-867-6630 endlcom@acm.org

# EXPRESSION OF SUPPORT BY MANUFACTURERS

The following member companies of the SFF Committee voted in favor of this industry specification.

EMC FCI Foxconn Hewlett Packard Sun Microsystems

The following member companies of the SFF Committee voted to abstain on this industry specification.

Adaptec Amphenol Dell Emulex Hitachi GST Infineon Intel LSI Logic Molex Seagate Toshiba America Tyco AMP Unisys Vitesse Semi If you are not a member of the SFF Committee, but you are interested in participating, the following principles have been reprinted here for your information.

#### PRINCIPLES OF THE SFF COMMITTEE

The SFF Committee is an ad hoc group formed to address storage industry needs in a prompt manner. When formed in 1990, the original goals were limited to defining de facto mechanical envelopes within which disk drives can be developed to fit compact computer and other small products.

Adopting a common industry size simplifies the integration of small drives (2 1/2" or less) into such systems. Board-board connectors carrying power and signals, and their position relative to the envelope are critical parameters in a product that has no cables to provide packaging leeway for the integrator.

In November 1992, the SFF Committee objectives were broadened to encompass other areas which needed similar attention, such as pinouts for interface applications, and form factor issues on larger disk drives. SFF is a forum for resolving industry issues that are either not addressed by the standards process or need an immediate solution.

Specifications created by the SFF Committee are expected to be submitted to bodies such as EIA (Electronic Industries Association) or an ASC (Accredited Standards Committee). They may be accepted for separate standards, or incorporated into other standards activities.

The principles of operation for the SFF Committee are not unlike those of an accredited standards committee. There are 3 levels of participation:

- Attending the meetings is open to all, but taking part in discussions is limited to member companies, or those invited by member companies

- The minutes and copies of material which are discussed during meetings are distributed only to those who sign up to receive documentation.

- The individuals who represent member companies of the SFF Committee receive documentation and vote on issues that arise. Votes are not taken during meetings, only guidance on directions. All voting is by letter ballot, which ensures all members an equal opportunity to be heard.

Material presented at SFF Committee meetings becomes public domain. There are no restrictions on the open mailing of material presented at committee meetings. In order to reduce disagreements and misunderstandings, copies must be provided for all agenda items that are discussed. Copies of the material presented, or revisions if completed in time, are included in the documentation mailings.

The sites for SFF Committee meetings rotate based on which member companies volunteer to host the meetings. Meetings have typically been held during the ASC T10 weeks.

The funds received from the annual membership fees are placed in escrow, and are used to reimburse ENDL for the services to manage the SFF Committee.

If you are not receiving the documentation of SFF Committee activities or are interested in becoming a member, the following signup information is reprinted here for your information.

Membership includes voting privileges on SFF Specs under development.

CD\_Access Electronic documentation contains:

- Minutes for the year-to-date plus all of last year

- Email traffic for the year-to-date plus all of last year

- The current revision of all the SFF Specifications, as well as any previous revisions distributed during the current year.

Meeting documentation contains:

- Minutes for the current meeting cycle.

- Copies of Specifications revised during the current meeting cycle.

Each electronic mailing obsoletes the previous mailing of that year e.g. July replaces May. To build a complete set of archives of all SFF documentation, retain the last SFF CD\_Access mailing of each year.

| Name:    |                                                     | Title:                              |          |      |                  |

|----------|-----------------------------------------------------|-------------------------------------|----------|------|------------------|

| Company: |                                                     |                                     |          |      |                  |

| Address: |                                                     |                                     |          |      |                  |

|          |                                                     |                                     |          |      |                  |

| Phone:   |                                                     | Fax:                                |          |      |                  |

| Email:   |                                                     |                                     |          |      |                  |

| Please   | register me with the SFF Comm                       | ittee for one y                     | ear.     |      |                  |

| Vot      | ing Membership w/Electronic d                       | ocumentation                        | \$2      | ,160 |                  |

| Vot      | ing Membership w/Meeting docu                       | mentation                           | \$ 1     | ,800 |                  |

| Nor      | -voting Observer w/Electronic                       | documentation                       | \$<br>\$ |      | U.S.<br>Overseas |

| Nor      | -voting Observer w/Meeting do                       | cumentation                         |          |      | U.S.<br>Overseas |

| Check F  | ayable to SFF Committee for \$                      | is En                               | closed   |      |                  |

| Please   | invoice me for \$ on                                | PO #:                               |          |      |                  |

| MC/Visa  | ./AmX                                               |                                     | Expires  |      |                  |

| 144      | ' Committee<br>26 Black Walnut Ct<br>atoga CA 95070 | 408-867-6<br>408-867-2<br>endlcom@a | 115Fx    |      |                  |

#### Foreword

When 2 1/2" diameter disk drives were introduced, there was no commonality on external dimensions e.g. physical size, mounting locations, connector type,

connector location, between vendors.

The first use of these disk drives was in specific applications such as laptop portable computers in which space was at a premium and time to market with the latest machine was an important factor. System integrators worked individually with vendors to develop the packaging. The result was wide diversity, and with space being such a major consideration in packaging, it was not possible to replace one vendor's drive with a competitive product.

The desire to reduce disk drive sizes to even smaller dimensions such as 1.8" and 1.3" made it likely that devices would become even more constrained in dimensions because of a possibility that such small devices could be inserted into a socket, not unlike the method of retaining semiconductor devices.

The problems faced by integrators, device suppliers, and component suppliers led to the formation of an industry ad hoc group to address the marketing and engineering considerations of the emerging new technology in disk drives. After two informal gatherings on the subject in the summer of 1990, the SFF Committee held its first meeting in August.

During the development of the form factor definitions, other activities were suggested because participants in the SFF Committee faced problems other than the physical form factors of disk drives. In November 1992, the members approved an expansion in charter to address any issues of general interest and concern to the storage industry. The SFF Committee became a forum for resolving industry issues that are either not addressed by the standards process or need an immediate solution.

At the same time, the principle was adopted of restricting the scope of an SFF project to a narrow area, so that the majority of specifications would be small and the projects could be completed in a rapid timeframe. If proposals are made by a number of contributors, the participating members select the best concepts and uses them to develop specifications which address specific issues in emerging storage markets.

Those companies which have agreed to support a specification are identified in the first pages of each SFF Specification. Industry consensus is not an essential requirement to publish an SFF Specification because it is recognized that in an emerging product area, there is room for more than one approach. By making the documentation on competing proposals available, an integrator can examine the alternatives available and select the product that is felt to be most suitable.

Suggestions for improvement of this specification will be welcome. They should be sent to the SFF Committee, 14426 Black Walnut Ct, Saratoga, CA 95070.

The development work on this specification was done by the SFF Committee, an industry group. The membership of the committee since its formation in 1990 has included a mix of companies which are leaders across the industry.

#### SFF Committee --

Signal Specification Architecture for HSS Links

1. Scope

Connections between end points in high speed serial data and communication systems, sometimes called links, are often made from several components like connectors, bulk cable, optical fiber, cable assemblies, transmitters, receivers. This document explores the issues and architectures that apply when it is desirable to form the connection from components that are specified independently of other components in the same connection. This independence allows construction of a physical connection by assembling the components without needing to consider the actual properties of the other components (as long as the other components also comply with their independent specifications).

Independent specification of connection components allows suppliers of the components to design products that may be used in a variety of applications and may be 'field assembled' to other compliant components to form the complete connection. These properties not only facilitate higher volumes and competition for the components themselves but also allow significant reduction in the qualification and verification time required for the final connections.

The properties of components that produce the desired interoperability and interchangeability are several including mechanical, overall size, electrical properties, optical properties, environmental stability, safety, power consumption, reliability, color, cost, thermal properties, installability, serviceability, robustness and others. Many of the ideas brought forward in this document apply to several of these properties. However, the electrical properties and the optical properties are the main focus for this document.

This simple sounding goal of independent specification is far more complicated than it may first appear. Interactions between the components and the direction of signal flow provide first order impact to the independence desired.

One of the first things to address in realizing the stated goals is identifying the points in the connection that define the boundaries of the components. These points should map directly to the points where the link components may be assembled and disassembled. For purposes of this document attention is confined to points where separable connectors (electrical or optical) exist within the connection. In this context the requirements for specification of signal performance at these connectors are considered.

Much of the material in this document is derived from a presentation developed by the Fibre Channel physical group and is available on the T11 web site (www.T11.org) as document 04-024v6 and from the recently completed Methodologies for Jitter and Signal Quality Specification (MJSQ) that is also available on the T11 web site. Bill Ham, HP, is the editor for both of these documents.

The SFF Committee was formed in August, 1990 to broaden the applications for storage devices, and is an ad hoc industry group of companies representing system integrators, peripheral suppliers, and component suppliers.

# 2. SFF Specifications

There are several projects active within the SFF Committee. At the date of printing specification numbers had been assigned to the following projects. The status of Specifications is dependent on committee activities.

| F = Forwarded                                                                                                                                                                                                                                                                                                           | The specification has been approved by the members for forwarding to a formal standards body.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P = Published                                                                                                                                                                                                                                                                                                           | The specification has been balloted by members and is available as a published SFF Specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| A = Approved                                                                                                                                                                                                                                                                                                            | The specification has been approved by ballot of the members<br>and is in preparation as an SFF Specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| C = Canceled                                                                                                                                                                                                                                                                                                            | The project was canceled, and no Specification was Published.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| D = Development<br>E = Expired                                                                                                                                                                                                                                                                                          | The specification is under development at SFF.<br>The specification has been published as an SFF<br>Specification, and the members voted against re-<br>publishing it when it came up for annual review.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| e = electronic                                                                                                                                                                                                                                                                                                          | Used as a suffix to indicate an SFF Specification which<br>has Expired but is still available in electronic form<br>from SFF e.g. a specification has been incorporated<br>into a draft or published standard which is only<br>available in hard copy.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| i = Information                                                                                                                                                                                                                                                                                                         | The specification has no SFF project activity in progress,<br>but it defines features in developing industry<br>standards. The specification was provided by a company,<br>editor of an accredited standard in development, or an<br>individual. It is provided for broad review (comments<br>to the author are encouraged).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| s = submitted                                                                                                                                                                                                                                                                                                           | The document is a proposal to the members for consideration to become an SFF Specification.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Spec # Rev I                                                                                                                                                                                                                                                                                                            | ist of Specifications as of June 28, 2005                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| SFF-8000<br>INF-8001i E<br>INF-8002i E<br>SFF-8003 E<br>SFF-8004 E<br>SFF-8006 E<br>SFF-8007 E<br>SFF-8008 E<br>SFF-8009 4.1<br>SFF-8009 4.1<br>SFF-8010 E<br>INF-8011i E<br>SFF-8012 3.0<br>SFF-8013 E<br>SFF-8013 E<br>SFF-8014 C<br>SFF-8015 E<br>SFF-8015 E<br>SFF-8016 C<br>SFF-8017 E<br>SFF-8018 E<br>SFF-8019 E | SFF Committee Information<br>44-pin ATA (AT Attachment) Pinouts for SFF Drives<br>68-pin ATA (AT Attachment) for SFF Drives<br>SCSI Pinouts for SFF Drives<br>Small Form Factor 2.5" Drives<br>Small Form Factor 1.8" Drives<br>Small Form Factor 1.3" Drives<br>2mm Connector Alternatives<br>68-pin Embedded Interface for SFF Drives<br>Unitized Connector for Cabled Drives<br>Small Form Factor 15mm 1.8" Drives<br>ATA Timing Extensions for Local Bus<br>4-Pin Power Connector Dimensions<br>ATA Download Microcode Command<br>Unitized Connector for Rack Mounted Drives<br>SCA Connector for Rack Mounted Drives<br>SCA Connector for Rack Mounted SFF SCSI Drives<br>Small Form Factor 10mm 2.5" Drives<br>SCSI Wiring Rules for Mixed Cable Plants<br>ATA Low Power Modes<br>Identify Drive Data for ATA Disks up to 8 GB |

| INF-8020i E<br>SFF-8025 0.7<br>INF-8028i E<br>SFF-8029 E                                                                                                                                                                                                                                                                | ATA Packet Interface for CD-ROMs<br>SFF Committee Specification Categories<br>- Errata to SFF-8020 Rev 2.5<br>- Errata to SFF-8020 Rev 1.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| SFF-8030<br>SFF-8031<br>SFF-8032<br>INF-8033i<br>INF-8034i<br>INF-8035i<br>INF-8036i<br>INF-8038i<br>INF-8039i                                                                                                                       | 2.0<br>1.6<br>E<br>E<br>E<br>E<br>E<br>E<br>E                                                        | SFF Committee Charter<br>Named Representatives of SFF Committee Members<br>SFF Committee Principles of Operation<br>Improved ATA Timing Extensions to 16.6 MBs<br>High Speed Local Bus ATA Line Termination Issues<br>Self-Monitoring, Analysis & Reporting Technology<br>ATA Signal Integrity Issues<br>Intel Small PCI SIG<br>Intel Bus Master IDE ATA Specification<br>Phoenix EDD (Enhanced Disk Drive) Specification                                                                                                                                                                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SFF-8040<br>SFF-8041<br>SFF-8042<br>SFF-8043<br>SFF-8045<br>SFF-8046<br>SFF-8047<br>SFF-8048<br>SFF-8049                                                                                                                             | 1.2<br>C<br>E<br>4.7<br>E<br>C<br>C<br>E                                                             | 25-pin Asynchronous SCSI Pinout<br>SCA-2 Connector Backend Configurations<br>VHDCI Connector Backend Configurations<br>40-pin MicroSCSI Pinout<br>40-pin SCA-2 Connector w/Parallel Selection<br>80-pin SCA-2 Connector for SCSI Disk Drives<br>40-pin SCA-2 Connector w/Serial Selection<br>80-pin SCA-2 Connector w/Parallel ESI<br>80-conductor ATA Cable Assembly                                                                                                                                                                                                                                                                                                                               |

| INF-8050i<br>INF-8051i<br>INF-8052i<br>SFF-8053<br>SFF-8054<br>INF-8055i<br>SFF-8056<br>SFF-8057<br>SFF-8058<br>SFF-8059                                                                                                             | 1.0<br>E<br>5.5<br>0.2<br>E<br>C<br>E<br>E<br>E                                                      | Bootable CD-ROM<br>Small Form Factor 3" Drives<br>ATA Interface for 3" Removable Devices<br>GBIC (Gigabit Interface Converter)<br>Automation Drive Interface Connector<br>SMART Application Guide for ATA Interface<br>50-pin 2mm Connector<br>Unitized ATA 2-plus Connector<br>Unitized ATA 3-in-1 Connector<br>40-pin ATA Connector                                                                                                                                                                                                                                                                                                                                                               |

| SFF-8060<br>SFF-8061<br>SFF-8062<br>SFF-8064<br>SFF-8065<br>SFF-8066<br>SFF-8067<br>INF-8068i<br>SFF-8069                                                                                                                            | 1.1<br>E<br>C<br>C<br>3.4<br>E<br>E                                                                  | SFF Committee Patent Policy<br>Emailing drawings over the SFF Reflector<br>Rolling Calendar of SSWGs and Plenaries<br>Unshielded HD Cable/Board Connector System<br>40-pin SCA-2 Connector w/High Voltage<br>80-pin SCA-2 Connector w/High Voltage<br>40-pin SCA-2 Connector w/Bidirectional ESI<br>Guidelines to Import Drawings into SFF Specs                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                      |                                                                                                      | Fax-Access Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| INF-8070i<br>SFF-8072<br>SFF-8073<br>INF-8074i<br>SFF-8075<br>SFF-8076<br>INF-8077i<br>SFF-8078<br>SFF-8079<br>SFF-8080<br>SFF-8080<br>SFF-8082<br>SFF-8084<br>SFF-8085<br>SFF-8085<br>SFF-8087<br>SFF-8088<br>SFF-8089<br>INF-8090i | 1.2<br>C<br>1.0<br>1.0<br>-<br>3.1<br>C<br>1.7<br>E<br>5.1<br>0.2<br>0.9<br>1.2<br>1.3<br>1.2<br>1.3 | Fax-Access Instructions<br>ATAPI for Rewritable Removable Media<br>80-pin SCA-2 for Fibre Channel Tape Applications<br>20-pin SCA-2 for GBIC Applications<br>SFP (Small Formfactor Pluggable) Transceiver<br>PCI Card Version of SFP Cage<br>SFP Additional IDs<br>XFP (10 Gbs Small Form Factor Pluggable Module)<br>XFP-E<br>SFP Rate and Application Selection<br>ATAPI for CD-Recordable Media<br>Labeling of Ports and Cable Assemblies<br>0.8mm SFP Card Edge Connector Dimensioning<br>100 Mbs Small Formfactor Transceivers<br>Compact Multilane Series: Common Elements<br>Compact Multilane Series: Shielded<br>SFP Rate and Application Codes<br>ATAPI for Multimedia Devices (Mt Fuji5) |

| SFF-81111.3SFF-81222.6SFF-8123CSFF-81240.2                                                                                  | 1.8" (60x70mm) w/SCA-2 Connector<br>1.8" drive form factor (78x54mm)                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SFF-8131                                                                                                                    | 40mmx50mm Form Factor                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| SFF-8200e 1.1<br>SFF-8201 2.4<br>SFF-8212e 1.2<br>SFF-8221 C<br>SFF-8222 2.1<br>SFF-8223 2.4<br>SFF-8225 C                  | 2 1/2" drive form factor dimensions<br>2 1/2" drive w/SFF-8001 44-pin ATA Connector<br>Pre-Aligned 2.5" Drive >10mm Form Factor<br>2.5" Drive w/SCA-2 Connector                                                                                                                                                                                                                                                                                                                           |

| SFF-8300 1.2<br>SFF-8301 1.4<br>SFF-8302e 1.1<br>SFF-8323 1.4<br>SFF-8332e E<br>SFF-8337e E<br>SFF-8342e 1.3<br>INF-8350i E | <pre>3 1/2" drive form factors (all of 83xx family) 3 1/2" drive form factor dimensions 3 1/2" Cabled Connector locations 3 1/2" drive w/Serial Attachment Connector 3 1/2" drive w/80-pin SFF-8015 SCA Connector 3 1/2" drive w/SCA-2 Connector 3 1/2" drive w/Serial Unitized Connector 3 1/2" Packaged Drives</pre>                                                                                                                                                                    |

| SFF-8400 C<br>SFF-8401<br>SFF-8410 16.1<br>INF-8411 1.0<br>SFF-8412 12.2<br>SFF-8415 4.1<br>SFF-8416 15.0                   | VHDCI (Very High Density Cable Interconnect)<br>Optical Transceiver for Short-Reach Appens<br>High Speed Serial Testing for Copper Links<br>High Speed Serial Testing for Backplanes<br>HSOI (High Speed Optical Interconnect) Testing<br>HPEI (High Performance Electrical Interconnect)<br>HPEI Bulk Cable Measurement/Performance Reqmnts                                                                                                                                              |

| SFF-842011.1SFF-84212.4SFF-8422CSFF-8423CSFF-84240.5SFF-84251.4SFF-8426SFF-8429SFF-84291.1                                  | HSSDC-1 Shielded Connections<br>HSSDC-2 Shielded Connections<br>FCI Shielded Connections<br>Molex Shielded Connections<br>Dual Row HSSDC-2 Shielded Connections<br>Single Voltage 12V Drives<br>HSSDC Double Width<br>Signal Specification Architecture for HSS Links                                                                                                                                                                                                                     |

| SFF-8430 4.1<br>SFF-8431<br>SFF-8441 14.1<br>SFF-8448 0.4<br>SFF-8451 10.1<br>SFF-8452 3.1<br>SFF-8453<br>SFF-8454          | MT-RJ Duplex Optical Connections<br>SFP+<br>VHDCI Shielded Configurations<br>SAS Sideband Utilization<br>SCA-2 Unshielded Connections<br>Glitch Free Mating Connections for Multidrop Aps<br>Shielded High Speed Serial connectors<br>SCA-2 Enhanced HSS                                                                                                                                                                                                                                  |

| SFF-84601.2SFF-8464CSFF-84702.9SFF-8471CSFF-84729.5INF-8475i2.2SFF-84802.1SFF-84821.8SFF-8483CSFF-84841.6SFF-84850.5        | HSS Backplane Design Guidelines<br>Improved MM HSS Optical Link Performance<br>Multilane Copper Connector<br>ZFP Multilane Copper Connector<br>Diagnostic Monitoring Interface for Optical Xcvrs<br>XPAK Small Formfactor Pluggable Receiver<br>HSS (High Speed Serial) DB9 Connections<br>Unshielded Dual Port Serial Attachment Connector<br>External Serial Attachment Connector<br>Multilane Unshielded Serial Attachment Connector<br>Serial GPIO (General Purpose Input/Output) Bus |

SFF-8500e 1.15 1/4" drive form factors (all of 85xx family)SFF-8501e 1.15 1/4" drive form factor dimensionsSFF-8508e 1.15 1/4" ATAPI CD-ROM w/audio connectorsSFF-85231.45 1/4" drive w/Serial Attachment ConnectorSFF-85513.25 1/4" CD Drives form factorSFF-85521.15 1/4" 9.5mm/12.7mm Optical Drive Form FactorSFF-8572C5 1/4" Tape form factorSFF-8610CSDX (Storage Device Architecture)SFF-8617SAS Transition cables

3. Sources

Copies of ANSI standards or proposed ANSI standards may be purchased from Global Engineering.

| 15 Inverness Way East | 800-854-7179 or 303-792-2181 |

|-----------------------|------------------------------|

| Englewood             | 303-792-2192Fx               |

| CO 80112-5704         |                              |

Copies of SFF Specifications are available by joining the SFF Committee as an Observer or Member or by download at ftp://ftp.seagate.com/sff

| 14426 Black Walnut ( | Ct 408-867-6630x303 |

|----------------------|---------------------|

| Saratoga             | 408-867-2115Fx      |

| CA 95070             |                     |

#### TABLE OF CONTENTS

| 1. | Introduction                                                                | 11 |

|----|-----------------------------------------------------------------------------|----|

| 2. | A simple connection                                                         | 11 |

|    | 2.1 Overview                                                                | 11 |

|    | 2.2 Under the hood for the transmitter device and the receiver device       | 13 |

|    | 2.3 Definition of receiver sensitivity and receiver device sensitivity      | 14 |

| 3. | Basic signal performance properties                                         | 15 |

|    | 3.1 Introduction                                                            | 15 |

|    | 3.2 Differential electrical links                                           | 16 |

| 4. | Measurement architecture requirements                                       | 17 |

|    | 4.1 Introduction                                                            | 17 |

|    | 4.2 Relationship between signal compliance measurements at interoperabili   | ty |

|    | points and operation in systems                                             | 17 |

| 5. | The interoperability penalty and related issues                             | 18 |

| 6. | Compliance interconnect and standard receiver device methods                | 18 |

|    | 6.1 Compensation                                                            | 18 |

|    | 6.2 Transmitter device compensation                                         | 19 |

|    | 6.3 Interconnect compensation                                               | 20 |

|    | 6.4 Receiver device compensation                                            | 20 |

|    | 6.5 Multiple compensation functions in the same link                        | 21 |

| 7. | De-embedding connectors in test fixtures                                    | 22 |

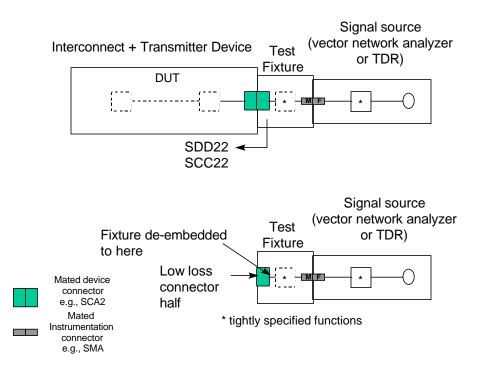

| 8. | Measurement conditions for signal output (DSO) at the transmitter device    | 23 |

| 9. | Measurement conditions for signal tolerance (DST) at the transmitter device | 24 |

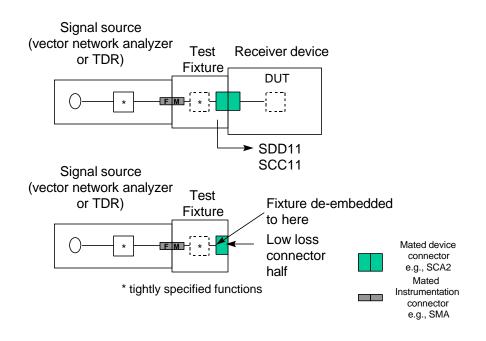

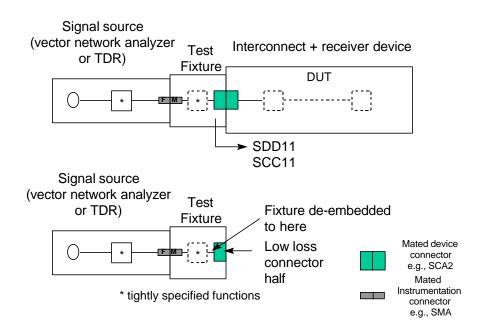

| 10 | . Measurement conditions for signal output (DSO) at the receiver device     | 25 |

| 11 | . Measurement conditions for signal tolerance (DST) at the receiver device  | 25 |

| 12 | . S-parameter measurements                                                  | 27 |

|    | 12.1 Introduction                                                           | 27 |

|    | 12.2 Naming conventions in high speed serial links                          | 27 |

|    | 12.3 Use of single ended instrumentation in differential applications       | 28 |

|    | 12.4 Measurement configurations for link elements                           | 30 |

|    | 12.4.1 Overview                                                             | 30 |

|    |                                                                             |    |

| 12.4.2 Transmitter device return loss                               | 31 |

|---------------------------------------------------------------------|----|

| 12.4.3 Receiver device return loss                                  | 32 |

| 12.4.4 S11 at the transmitter device connector (interconnect input) | 33 |

| 12.4.5 S22 at the receiver device connector (interconnect output)   | 34 |

| 12.5 Summary for S-parameter measurements                           | 34 |

| 13. Development of performance specification values                 | 35 |

| 14. Summary                                                         | 36 |

Signal Specification Architecture for Interoperable High Speed Serial Links

# 1. Introduction

Connections between end points in high speed serial data and communication systems, sometimes called links, are often made from several components like connectors, bulk cable, optical fiber, cable assemblies, transmitters, receivers. This document explores the issues and architectures that apply when it is desirable to form the connection from components that are specified independently of other components in the same connection. This independence allows construction of a physical connection by assembling the components without needing to consider the actual properties of the other components (as long as the other components also comply with their independent specifications).

Independent specification of connection components allows suppliers of the components to design products that may be used in a variety of applications and may be 'field assembled' to other compliant components to form the complete connection. These properties not only facilitate higher volumes and competition for the components themselves but also allow significant reduction in the qualification and verification time required for the final connections.

The properties of components that produce the desired interoperability and interchangeability are several including mechanical, overall size, electrical properties, optical properties, environmental stability, safety, power consumption, reliability, color, cost, thermal properties, installability, serviceability, robustness and others. Many of the ideas brought forward in this document apply to several of these properties. However, the electrical properties and the optical properties are the main focus for this document.

This simple sounding goal of independent specification is far more complicated than it may first appear. Interactions between the components and the direction of signal flow provide first order impact to the independence desired.

One of the first things to address in realizing the stated goals is identifying the points in the connection that define the boundaries of the components. These points should map directly to the points where components may be assembled and disassembled. For purposes of this document attention is confined to points where separable connectors (electrical or optical) exist within the connection. In this context the requirements for specification of signal performance at these connectors are considered.

Much of the material in this document is derived from a presentation developed by the Fibre Channel physical group and is available on the T11 web site (www.T11.org) as document 04-024v6 and from the recently completed Methodologies for Jitter and Signal Quality Specification (MJSQ) that is available from http://www.techstreet.com/cgi-bin/new\_results search for `MJSQ'. Bill Ham, HP, is the editor for both of these documents. Both FC-PI-2 and SAS 1.1 have adopted key portions of the methodology defined in this document.

# 2. A simple connection

# 2.1 Overview

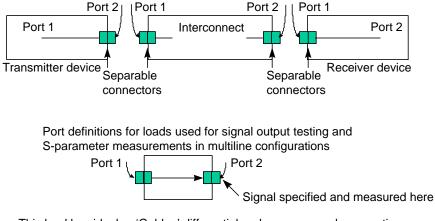

In a simple example, that becomes less simple soon enough, the connection, or physical link, consists of three component parts: the transmitter device, the interconnect, and the receiver device each joined together by a separable connector. Each component part needs its own performance specification that is independent of the properties of any other specific component in the connection. Signals travel in

opposite directions down the same nominal path if a duplex connection is used. For some applications like Gigabit Ethernet the same wire is used simultaneously for both directions (the received signal is detected by subtracting the known launched signal from the total). This document is optimized for the more common case where each direction of signal travel has its own dedicated wires. The general approach is useful in both cases.

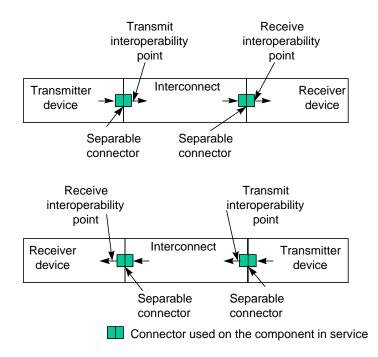

Figure 1 shows a simple duplex link and the location of the connectors.

Figure 1 -A simple duplex link physical connection

Since connectors are always used in the mated condition the only access to the signals is before the signal enters the mated connector (i.e. upstream) or after the signal exits the connector (i.e. downstream). Even if signals could be practically accessed at the point of mating within the connector such access would disturb the connector to the point that the measurement of the signal would be compromised. Attempting to access the unmated connector with probes, for example, is also not acceptable because the connector is not the same when unmated as when mated and the probe contact points will not be at the same location as the connector contact points. When using probes the contacts are not deflected and the shields are not connected in unmated electrical connectors. For optical connectors the only practical access method to an unmated connector is by adding the mating half and that makes it a mated connector.

In this document the signal outputs are always measured downstream of the mated connector (as shown in Figure 1) so that the contribution of the connector to the signal properties is included in the measurement. This approach assigns a portion of the connector losses to the upstream component but it also makes the signal measurement conservative. If the connectors on both ends of the interconnect are the same, the additional loss at the downstream connector is balanced by the reduced loss at the upstream connector. For transmitter devices a slightly stronger transmitter is required to pass the signal through the downstream half of the connector that does not belong to the transmitter device. The signal coming into receiver devices is specified after the signal has passed through the connector.

Examination of the details of the measurement methods described later shows that the mated connector issue is not a severe as it may appear.

Each part intrinsically has some properties that may be expressed via impedance and/or S parameter methodologies

The TxRx connection has an assumed 'reference impedance' e.g. 100 ohms.

#### 2.2 Under the hood for the transmitter device and the receiver device

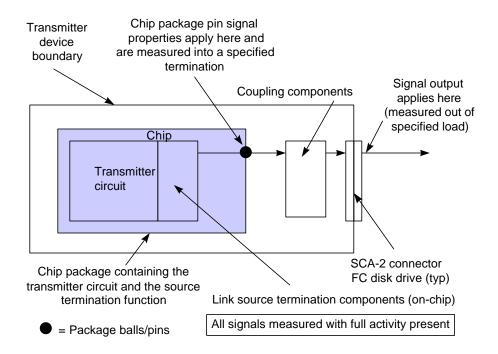

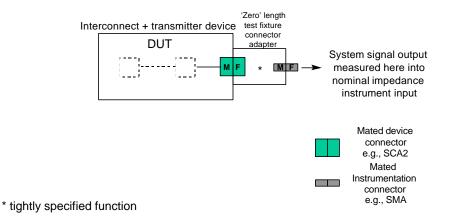

Figure 2 - Transmitter device details for an HDD type interoperability point

Figure 2 shows the details of a transmitter device. Notice that there are at least three internal parts of this transmitter device that could be called a 'transmitter':

- 1. the transmitter circuit in the chip

- 2. the chip itself

- 3. the chip and its associated chip package

The term `transmitter' is therefore not well defined and is not used in the terminology without a modifier.

The transmitter device contains a connector (half a mated pair), optional coupling circuits, the source termination, the transmitter circuit, PCB traces and vias, the chip package, and possibly ESD devices. It is assumed that the source termination is contained within the chip package.

Signal Specification Architecture for HSS Links

Interoperability specifications are defined at the connector of the transmitter device for storage standards (FC, SAS, SSA etc.)

Interoperability points might be defined at the chip package pins in some network standards (e. g., Ethernet XAUI).

The practice of defining interoperability points at the chip pins optimizes the specification from a chip point of view but may leave the rest of the interoperability problem in the link unspecified. This document assumes that the more important interoperability points are at the separable connectors where the user interfaces exist rather than at the chip interfaces that are usually permanently embedded inside some device. Other problems with specifying signals at chip pins include practical measurement difficulties and the impact of getting the signal to and through the transmitter device connector.

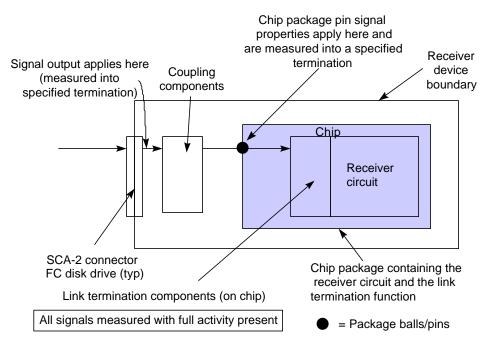

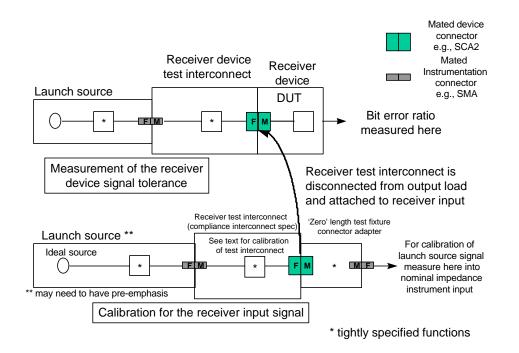

Figure 3 shows the details of a receiver device. It is similar to the transmitter device.

Figure 3 - Receiver device details for an HDD type interoperability point

Notice that there are at least three internal parts of this receiver device that could be called a `receiver':

- 1. the receiver circuit in the chip

- 2. the chip itself

- 3. the chip and its associated chip package

The term 'receiver' is therefore not well defined and is not used in the terminology without a modifier.

The receiver device contains a connector (half a mated pair), optional coupling circuits, the link termination, the receiver circuit, PCB traces and vias, the chip package, and possibly ESD devices. It is assumed that the link termination is contained within the chip package.

Signal Specification Architecture for HSS Links

# 2.3 Definition of receiver sensitivity and receiver device sensitivity

The term 'receiver sensitivity' is problematic in common usage. This term is not used for interoperability specifications but it has proven impossible to purge the term. A related term applicable to the receiver device input signal is the 'receiver device sensitivity'. While these two terms are related they are significantly different because of the noise environment assumed. The following description is used to uniquely define these terms with the understanding that this document discourages usage of either term.

## Receiver sensitivity:

- The receiver in the receiver sensitivity refers to signal properties at the chip package pin for the chip package that contains the receiver circuit.

- Receiver sensitivity is defined as the minimum vertical inner eye opening at which the receiver chip delivers the required BER the horizontal eye opening shall be minimum (maximum jitter present) and all activity is **<u>quiesced</u>** except for the receiver itself.

- Receiver sensitivity is not defined where there are no chip pin specifications

## Receiver device sensitivity:

The term 'receiver device sensitivity' is defined as the minimum vertical inner eye opening at which the receiver chip (the chip in the chip package on the board containing the receive device interoperability point) delivers the required BER with all activity expected in the application for the receiver circuit present (not quiesced as for the receiver sensitivity definition), with the CJTPAT (see MJSQ), and the minimum horizontal eye opening in the signal at the receive device interoperability point.

Special test conditions are required to measure these sensitivities as described later. The terminology used is 'signal tolerance' instead of 'receiver sensitivity'.

## 3. Basic signal performance properties

# 3.1 Introduction

At any given interoperability point a set of signal or link performance requirements are used to define the interoperability requirements. If these requirements are all met then, within the limitations of specific system implementation noise properties and damage that may have occurred during shipping and installation, the complete link should deliver the require BER without further testing and qualification.

For both optical and electrical links the following signal properties require specification at every interoperability point:

- Signal output (eye type measurement of the signal output at the interoperability point)

- Downstream signal tolerance (BER measurement using minimum quality signal as input at the interoperability point)

- Upstream return loss (S parameter 22 looking upstream at the interoperability point)

- Downstream return loss (S parameter 11 looking downstream at the interoperability point)

The details of these measurements depend strongly on the details of the electrical or optical connection.

In this document only the differential electrical type is described since that is the most complex. Single ended electrical and optical types essentially use the differential signal measurement in a single ended mode.

# 3.2 Differential electrical links

At a differential electrical interoperability point both the differential and common mode performance requirements are specified. The complete list of the eight required properties is in Table 1.

| Table 1 - List          | of specifications | required at | differential | electrical |  |  |  |  |

|-------------------------|-------------------|-------------|--------------|------------|--|--|--|--|

| interoperability points |                   |             |              |            |  |  |  |  |

| L_                                                                                                  |            |                                                                     |  |  |  |

|-----------------------------------------------------------------------------------------------------|------------|---------------------------------------------------------------------|--|--|--|

| Name                                                                                                | Symbol     | Description                                                         |  |  |  |

| Differential signal                                                                                 | DSO        | Jitter eye measurement (Note 1) with defined data pattern out of a  |  |  |  |

| output                                                                                              |            | laboratory grade electrical load - signal measured through the      |  |  |  |

|                                                                                                     |            | mated connector used in service                                     |  |  |  |

|                                                                                                     |            | Measures the performance of all upstream portions of the link       |  |  |  |

| Differential signal                                                                                 | DST        | BER measurement with a defined data pattern using a signal          |  |  |  |

| tolerance                                                                                           | (Note 2)   | generated from laboratory grade calibration and launch conditions - |  |  |  |

|                                                                                                     | (Note 3)   | signal calibrated through a laboratory grade mated connector        |  |  |  |

|                                                                                                     |            | Measures the performance of all downstream portions of the link     |  |  |  |

| Differential upstream                                                                               | SDD22      | Return loss measurement looking upstream using differential S       |  |  |  |

| return loss                                                                                         |            | parameter methodologies assuming an ideal differential and common   |  |  |  |

| (Note 4)                                                                                            |            | mode reference impedance - effects of the service connector are     |  |  |  |

| (                                                                                                   |            | included in this measurement                                        |  |  |  |

|                                                                                                     |            | Measures the performance of all upstream portions of the link       |  |  |  |

| Differential                                                                                        | SDD11      | Return loss measurement looking downstream using differential S     |  |  |  |

| downstream return loss                                                                              |            | parameter methodologies assuming an ideal differential and common   |  |  |  |

| (Note 4)                                                                                            |            | mode reference impedance - effects of the service connector are     |  |  |  |

| (                                                                                                   |            | included in this measurement                                        |  |  |  |

|                                                                                                     |            | Measures the performance of all downstream portions of the link     |  |  |  |

| Common mode signal                                                                                  | CSO        | Jitter eye measurement (Note 1) with defined data pattern out of a  |  |  |  |

| output                                                                                              | CBU        | laboratory grade electrical load - signal measured through the      |  |  |  |

| ομεραί                                                                                              |            | mated connector used in service                                     |  |  |  |

|                                                                                                     |            |                                                                     |  |  |  |

| <u></u>                                                                                             |            | Measures the performance of all upstream portions of the link       |  |  |  |

| Common mode signal                                                                                  | CST        | BER measurement with a defined data pattern using a signal          |  |  |  |

| tolerance                                                                                           |            | generated from laboratory grade calibration and launch conditions - |  |  |  |

|                                                                                                     | (Note 3))  | signal calibrated through a laboratory grade mated connector        |  |  |  |

|                                                                                                     |            | Measures the performance of all downstream portions of the link     |  |  |  |

| Common mode upstream                                                                                | SCC22      | Return loss measurement looking upstream using common mode S        |  |  |  |

| return loss                                                                                         |            | parameter methodologies assuming an ideal differential and common   |  |  |  |

| (Note 4)                                                                                            |            | mode reference impedance - effects of the service connector are     |  |  |  |

|                                                                                                     |            | included in this measurement                                        |  |  |  |

|                                                                                                     |            | Measures the performance of all upstream portions of the link       |  |  |  |

| Common mode downstream                                                                              | SCC11      | Return loss measurement looking downstream using common mode S      |  |  |  |

| return loss                                                                                         |            | parameter methodologies assuming an ideal differential and common   |  |  |  |

| (Note 4)                                                                                            |            | mode reference impedance - effects of the service connector are     |  |  |  |

|                                                                                                     |            | included in this measurement                                        |  |  |  |

|                                                                                                     |            | Measures the performance of all downstream portions of the link     |  |  |  |

| Note 1 - see MJSQ for (                                                                             | details or | n jitter eye measurements                                           |  |  |  |

| Note 2 - Signal tolera:                                                                             | nce measur | cements for differential and common mode properties cannot be       |  |  |  |

| separated because the :                                                                             | result of  | a tolerance measurement is the BER for the link. The signal used    |  |  |  |

| for signal tolerance m                                                                              | easurement | s contains the worst case combination of differential, common mode, |  |  |  |

| and data pattern prope                                                                              | rties.     |                                                                     |  |  |  |

| The differential and c                                                                              | ommon mode | e content in the signal used for signal tolerance is the specified  |  |  |  |

| quantity in this table.                                                                             |            |                                                                     |  |  |  |

| Note 3 - Signal tolera:                                                                             | nce method | ls are described in more detail in MJSQ where four kinds of jitter  |  |  |  |

| content are described in these signals.                                                             |            |                                                                     |  |  |  |

| Note 4 - Use of S parameters assumes that the relevant portions of the links behave linearly - such |            |                                                                     |  |  |  |

| behavior may not always exist in active devices or where magnetic coupling elements are used - the  |            |                                                                     |  |  |  |

|                                                                                                     |            | nominal bias conditions during this measurement to minimize the     |  |  |  |

| impact of non-linear p                                                                              |            |                                                                     |  |  |  |

| - · · · · · · · · · · · ·                                                                           | ÷          |                                                                     |  |  |  |

# 4. Measurement architecture requirements

## 4.1 Introduction

Signal specifications are only meaningful if the signals can be measured with practical instrumentation. Another requirement is that different laboratories making measurements on the same signal get the same results within acceptable measurement error. In other words the measurements must be accessible, verifiable, and transportable. As of this writing there are no accepted standards for creating signals with traceable properties and with all the properties required for an effective signal specification architecture for high speed serial applications.

Some of the elements required for practical, verifiable, and transportable signal measurements are included in this document.

Having signal specifications at interoperability points that do not depend on the actual properties of the other link components not under test requires that specified known loads be used for the signal measurements. In service, the load presented to the interoperability point will be that of the actual component and environment existing in service.

Interfacing with practical instruments also requires that specified impedance environments be used. This forces a signal measurement architecture where the impedance environment is 50 or possibly 75 ohms single ended (100 or 150 ohms differential). It also forces the requirement for instrumentation quality loads of the correct value.

Instrumentation quality loads are readily available for simple transmission line termination. For more complex loads the industry is still working on how to make these available. The properties of more complex loads include specified propagation time, insertion loss properties, crosstalk properties, and jitter creation properties. More discussion on the complex loads is given in clause 6.

For signal tolerance measurements one must calibrate the signal before applying it to the interoperability point under test. This calibration is done by adjusting the properties of the signal measured out of a known load (just like the signal output case) and then removing the known load and applying the signal unchanged to the interoperability point under test. It is assumed that any changes to the signal from the calibration state to the measurement state are caused by the interoperability point under test and is therefore part of the performance sought by the measurement.

# 4.2 Relationship between signal compliance measurements at interoperability points and operation in systems

The signal and return loss measurements in this document apply under specified test conditions that simulate some parts of the conditions existing in service. This simulation includes, for example, duplex traffic on all Ports and under all applicable environmental conditions. Other features existing in service, such as non ideal return loss in parts of the link that are not present when measuring signals in the specified test conditions, are accounted for in the specifications themselves. This methodology is required to give each side of the interoperability point signal performance requirements that do not depend on knowing the properties of the other side.

Measuring signals in an actual functioning system at an interoperability point does

not verify compliance for the components on either side of the interoperability point. Such a measurement may verify that the specific combination of components in the system at the time of the measurement produces compliant signals. Interaction between components on either side of the interoperability point may allow the signal measured to be compliant but this compliance may have resulted because one component is out of specification while the other is better than required.

It is recommended that additional margin be allowed when performing signal compliance measurements to account for conditions existing in service that may not have been accounted for in the specified measurements and specification limits.

#### 5. The interoperability penalty and related issues

There is an interoperability penalty in the signal specifications caused by differences in the signal output and signal tolerance at the same interoperability point. These differences arise because components on both sides of the interoperability point each are allowed independent tolerances for properties.

For example, in a simple d.c. system with two compliant components, if the downstream component has a lower impedance than nominal and the upstream component has a higher impedance than nominal the signal at the interface is reduced by both the upstream and downstream components. If the signal output specification is measured with nominal impedance for the signal load the effect of the high impedance on the upstream component is included in the measurement. However, the signal will still not meet the minimum amplitude requirement when a compliant, but not nominal, low impedance downstream component is used in service.

The output signal specification is increased to accommodate the worst case possible from compliant components. This increase is effectively an interoperability penalty that would not exist if nominal components were used.

This document does not specify the methodology for determining the interoperability penalty values as this is a complex topic that has not yet been documented in detail. Extensive use of sophisticated simulations are required for determining the interoperability penalty in specific cases.

Another somewhat related issue is the applicability of the measurements to applications where small differences exist between the measurement conditions and the service conditions. For example, the actual link length between the transmitter device and the receiver device may be different from the cable assembly length assumed or used during measurement because of board traces between the cable assembly and the link termination in the system.

One approach used to address this condition for electrical interconnect assemblies in SFF-8415 (see www.sffcommittee.com) requires that eye measurements on interconnect assemblies be valid at data rates 10% above and 10% below the nominal data rate as well as at the nominal data rate. This ensures that there are no important suckouts near the data rate.

## 6. Compliance interconnect and standard receiver device methods

# 6.1 Compensation

Compensation is the attempt to mitigate the deleterious effects occurring during signal transmission by adding or subtracting features from the signal. Compensation may be executed in the transmitter device, in the interconnect, and in the receiver

device. Compensation may be applied to properties of the signal that depend on the specific data pattern and to properties that are predictable upon subsequent use such as line to line propagation time skew and DCD. The basic assumption for compensation is that the degradation intensity and type remains stable over periods of at least several bit times.

Compensation schemes that may adjust the parameters of the compensating mechanism are termed "adjustable". Compensation schemes that use active circuitry are termed "active". Compensation schemes that pass the signal through a transfer function are termed "filtered" or "equalized", the latter being derived from the common practice of matching the transmission losses across part of the frequency spectrum. Adjustable schemes that change the parameters of the compensating mechanism in response to specific received signal measurements are termed "adaptive". It is usually assumed that adaptive schemes will use some sort of automatic means to do the adapting.

The mechanisms of degrading signals fall broadly into two modes: (1) primary losses along the transmission path such as attenuation, reflections, and resonances and (2) secondary losses due to causes that are external to the transmission path such as crosstalk noise. In some cases the secondary losses may exceed the primary losses. Losses may be amplitude or timing precision or both.

Details concerning the important differences between the location of the compensation are explored in the following sub clauses.

## 6.2 Transmitter device compensation

Any compensation scheme that is implemented in the transmitter device either (a) makes assumptions concerning the nature and intensity of the degradation that occurs during the transmission or (b) has some sort of feedback from the receiver that allows adjustment of the parameters of the compensation scheme. Such a feedback mechanism relies on higher level protocol.

When transmitter device compensation is used, the results are visible in the signal launched from the transmitter device. However, it may be necessary to use special methods to determine the quality of the signal from the transmitter device since the compensation process may significantly alter the signal.

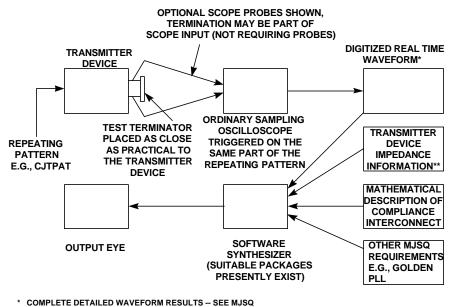

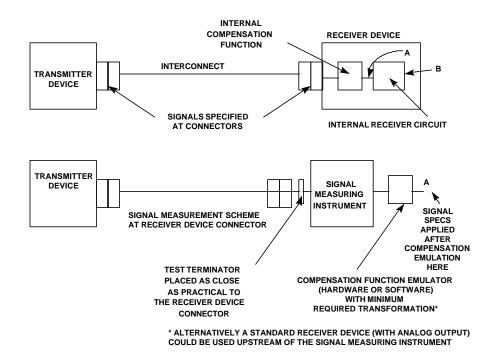

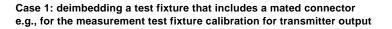

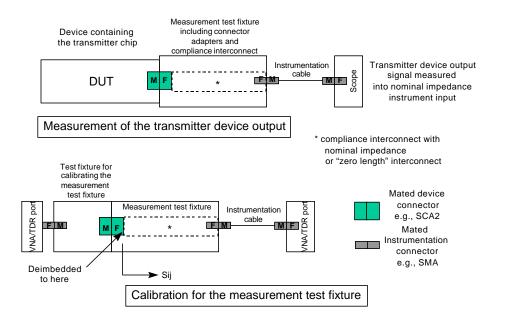

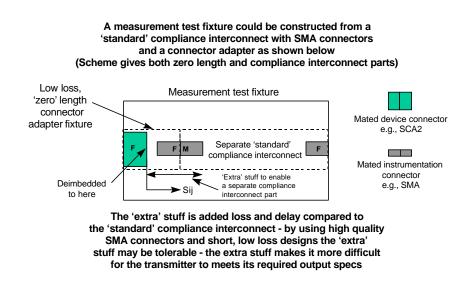

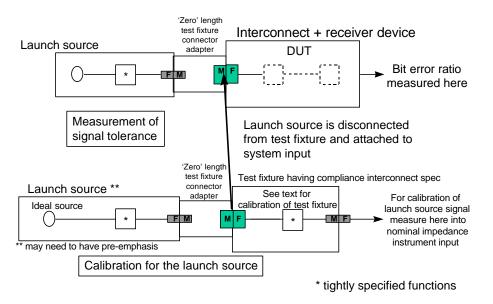

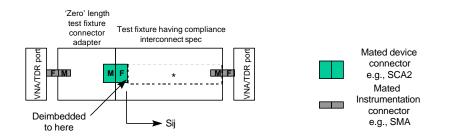

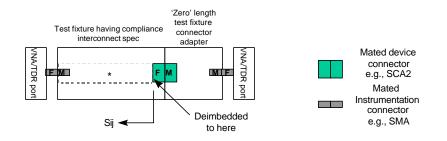

The general method for verifying transmitter device compensation is to pass the transmitter device signal through a transfer function that emulates the loss mechanism, in both magnitude and phase, for a standard interconnect (called a compliance interconnect) attached to the transmitter device before examining the signal. One measurement set up for such a methodology is shown in Figure 4 where models are used instead of hardware where possible.

The mathematical description of a compliance interconnect is not a specification for the interconnect used in the system itself (although the specifications for the compliance interconnect are derived from assumptions about the system interconnect); it is a specification of the load that is placed on the transmitter device for purposes of enabling measurement of transmitter device signals. See T11/04-604v0 for a more detailed discussion of compliance interconnect methodologies.

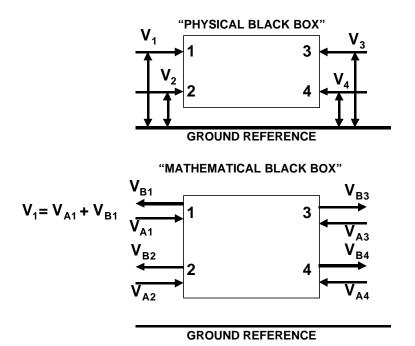

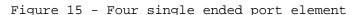

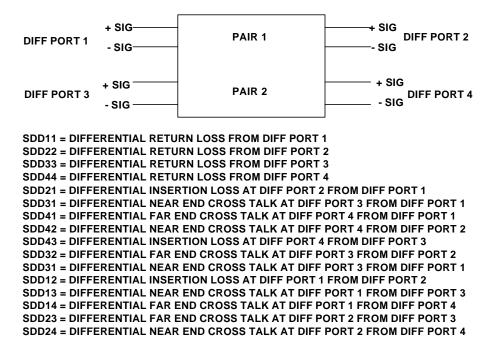

\*\* OBTAINED FROM A SEPARATE MEASUREMENT ON THE TRANSMITTER

Figure 4 - Measurement set up for evaluating transmitters