SFF Committee documentation may be purchased in electronic form. SFF specifications are available at ftp://ftp.seagate.com/sff

SFF Committee

SFF-8419

Specification for

# SFP+ Power and Low Speed Interface

Rev 1.3 June 11, 2015

Secretariat: SFF Committee

Abstract: This specification defines the low speed electrical and management interface specifications for SFP+ (enhanced Small Formfactor Pluggable) modules and hosts. The SFP+ module is a hot pluggable small footprint serial-to-serial dataagnostic optical transceiver.

This specification provides a common reference for systems manufacturers, system integrators, and suppliers. This is an internal working specification of the SFF Committee, an industry ad hoc group.

This specification is made available for public review, and written comments are solicited from readers. Comments received by the members will be considered for inclusion in future revisions of this specification.

Support: This specification is supported by the identified member companies of the SFF Committee.

### POINTS OF CONTACT:

Chairman SFF Committee

I. Dal Allan

ENDL

14426 Black Walnut Court

Saratoga CA 95070

408-867-6630

endlcom@acm.org

#### EXPRESSION OF SUPPORT BY MANUFACTURERS

The following member companies of the SFF Committee voted in favor of this industry specification:

Amphenol JDS Uniphase Arista OLogic

Broadcom Shinning Electronics

Finisar Sichuan GLGnet Electronics Sumitomo

Hewlett Packard TE Connectivity

**HGST**

The following member companies of the SFF Committee voted against this industry specification.

Foxconn Mellanox

The following member companies of the SFF Committee voted to abstain on this industry specification.

EMC Seagate

FCI

The user's attention is called to the possibility that implementation to this Specification may require use of an invention covered by patent rights. By distribution of this specification, no position is taken with respect to the validity of a claim or claims or of any patent rights in connection therewith. Members of the SFF Committee which advise that a patent exists are required to provide a statement of willingness to grant a license under these rights on reasonable and non-discriminatory terms and conditions to applicants desiring to obtain such a license.

### **Change History:**

Rev 1.0 March 31, 2015

- Content derived from SFF-8431 Rev 4.2 Sections 2.1-2.7 and 4

- Updated with current template, but modified numbering to retain Section 2 as the beginning of technical content as per SFF-8431 and retained sequential Table/Figure numbering instead of within section.

- Converted symbols to text and editorial corrections made to case, consistency of expression, etc.

- Corrected references to SFF-8083 to be SFF-8071

Rev 1.1 May 8, 2015

- Added cross-references to SFF-8431 sections/tables/figures

Rev 1.2 May 29, 2015

- Corrected references to SFP+ Module Power Supply Requirements in Section 2.6. Rev 1.3 June 3, 2015

- Transferred power supply Section 2 and Appendix D.17 from SFF-8418

- Title changed to reflect the transferred content

#### Foreword

The development work on this specification was done by the SFF Committee, an industry group. The membership of the committee since its formation in August 1990 has included a mix of companies which are leaders across the industry.

When 2 1/2" diameter disk drives were introduced, there was no commonality on external dimensions e.g. physical size, mounting locations, connector type, connector location, between vendors.

The first use of these disk drives was in specific applications such as laptop portable computers and system integrators worked individually with vendors to develop the packaging. The result was wide diversity, and incompatibility.

The problems faced by integrators, device suppliers, and component suppliers led to the formation of the SFF Committee as an industry ad hoc group to address the marketing and engineering considerations of the emerging new technology.

During the development of the form factor definitions, other activities were suggested because participants in the SFF Committee faced more problems than the physical form factors of disk drives. In November 1992, the charter was expanded to address any issues of general interest and concern to the storage industry. The SFF Committee became a forum for resolving industry issues that are either not addressed by the standards process or need an immediate solution.

Those companies which have agreed to support a specification are identified in the first pages of each SFF Specification. Industry consensus is not an essential requirement to publish an SFF Specification because it is recognized that in an emerging product area, there is room for more than one approach. By making the documentation on competing proposals available, an integrator can examine the alternatives available and select the product that is felt to be most suitable.

SFF Committee meetings are held during T10 weeks (see www.t10.org), and Specific Subject Working Groups are held at the convenience of the participants. Material presented at SFF Committee meetings becomes public domain, and there are no restrictions on the open mailing of material presented at committee meetings.

Most of the specifications developed by the SFF Committee have either been incorporated into standards or adopted as standards by EIA (Electronic Industries Association), ANSI (American National Standards Institute) and IEC (International Electrotechnical Commission).

If you are interested in participating or wish to follow the activities of the SFF Committee, the signup for membership and/or documentation can be found at:

www.sffcommittee.com/ie/join.html

The complete list of SFF Specifications which have been completed or are currently being worked on by the SFF Committee can be found at:

ftp://ftp.seagate.com/sff/SFF-8000.TXT

If you wish to know more about the SFF Committee, the principles which guide the activities can be found at:

ftp://ftp.seagate.com/sff/SFF-8032.TXT

Suggestions for improvement of this specification will be welcome. They should be sent to the SFF Committee, 14426 Black Walnut Ct, Saratoga, CA 95070.

| Cross Reference of Sections, Figures and Tables                      | 8431   | Section   |

|----------------------------------------------------------------------|--------|-----------|

| Industry Documents                                                   |        | 1.1.1     |

| Introduction                                                         | 1.1    | 3.1       |

| Low Speed Electrical and Power Specifications                        | 2      | 2         |

| SFP+ 2-Wire Interface                                                | 4      | 5         |

|                                                                      | Figure |           |

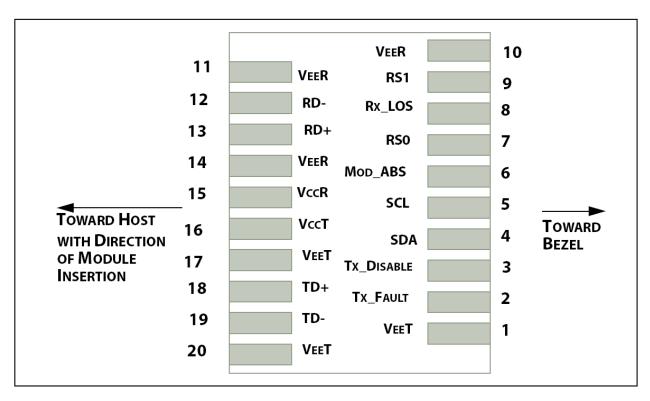

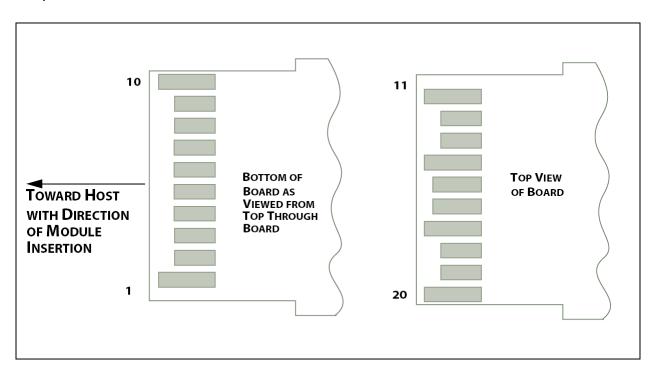

| Host PCB SFP+ pad assignment top view                                | 1      | Figure 2  |

| SFP+ Module Contact Assignment                                       | 2      | Figure 3  |

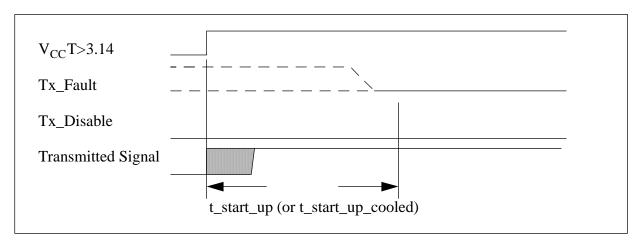

| Power On Initialization of Module, Tx_Disable Negated                | 3      | Figure 4  |

| Power On Initialization of Module, Tx_Disable Asserted               | 4      | Figure 5  |

| Example of Initialization During Hot Plugging, Tx_Disable Negated    | 5      | Figure 6  |

| Management of Module During Normal Operation, Tx_Disable Implemented | 6      | Figure 7  |

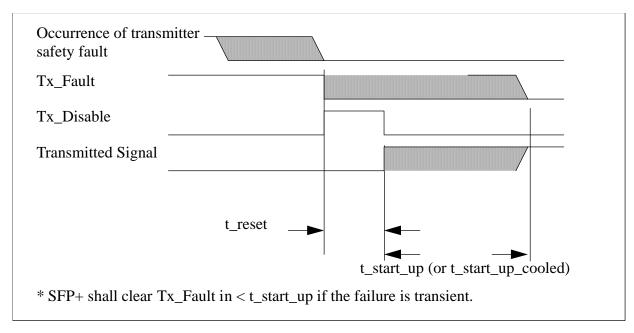

| Occurrence of Condition Generating Tx_Fault                          | 7      | Figure 8  |

| Successful Recovery from Transient Safety Fault Condition            | 8      | Figure 9  |

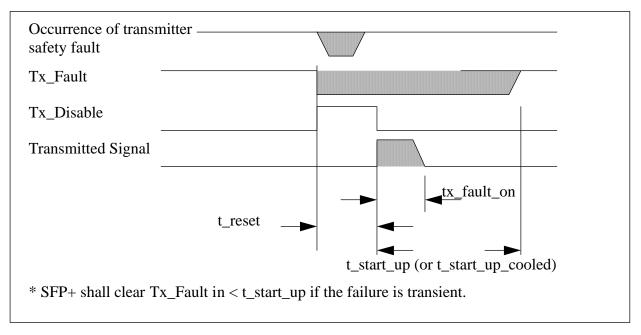

| Unsuccessful recovery from Safety Fault Condition                    | 9      | Figure 10 |

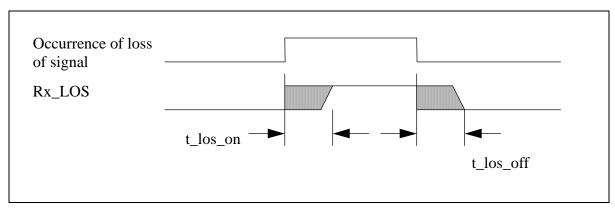

| Timing of Rx_LOS Detection                                           | 10     | Figure 11 |

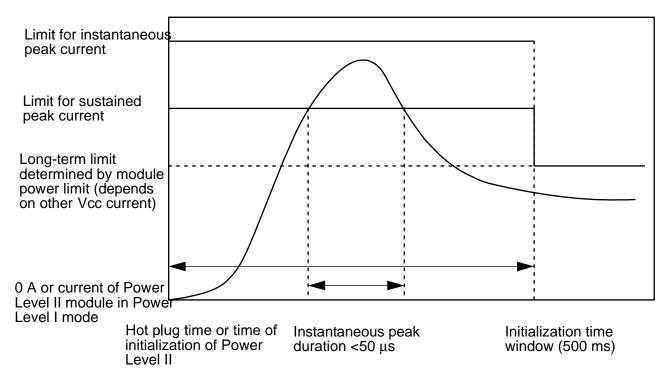

| Instantaneous and Sustained Peak Current for VccT or VccR            | 11     | Figure 1  |

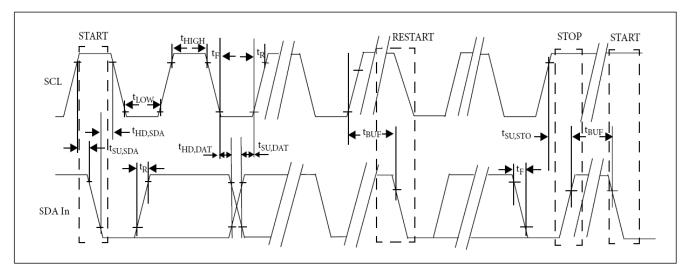

| 2-Wire Timing Diagram                                                | 25     | Figure 12 |

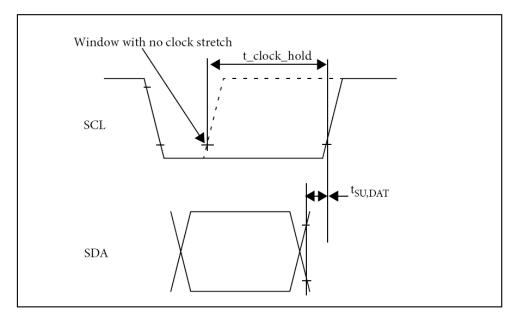

| Detail of Clock Stretching                                           | 26     | Figure 13 |

| Current Address Read Operation                                       | 27     | Figure 14 |

| Random Read                                                          | 28     | Figure 15 |

| Sequential Address Read Starting at Current Word Address             | 29     | Figure 16 |

| Sequential Address Read Starting with Random Read                    | 30     | Figure 17 |

| SFP+ Write Byte Operation                                            | 31     | Figure 18 |

| Sequential Write Operation                                           | 32     | Figure 19 |

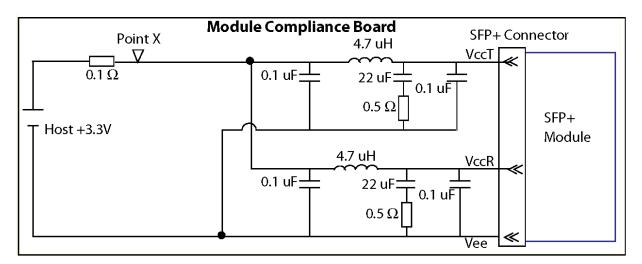

| Module Compliance Board Power Supply Filters                         | 56     | Figure 20 |

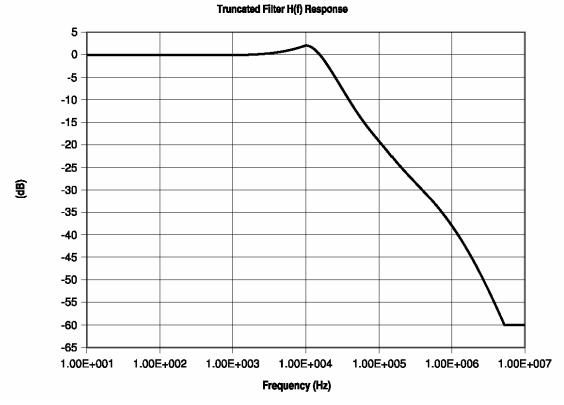

| Reference Filter Response                                            | 57     | Figure 21 |

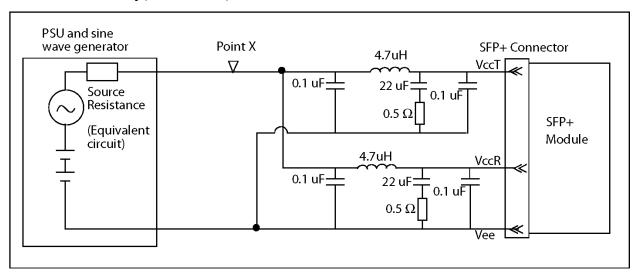

| Power Supply Noise Tolerance Test Setup                              | 58     | Figure 22 |

|                                                                      | Table  |           |

| SFP+ Module and Host Electrical contact definition                   | 3      | Table 2   |

| Rate Select Hardware Control Contacts                                | 4      | Table 3   |

| Low Speed Module Electrical Specifications                           | 5      | Table 4   |

| Low Speed Host Electrical Specifications                             | 6      | Table 5   |

| Timing Parameters for SFP+ Management                                | 7      | Table 6   |

| SFP+ Module Power Supply Requirements                                | 8      | Table 1   |

| 2-Wire Interface Electrical Specifications                           | 21     | Table 7   |

| SFP+ 2-Wire Timing Specifications                                    | 22     | Table 8   |

| SFP+ Memory Specifications                                           | 23     | Table 9   |

| SFP+ Device Address Word                                             | 24     | Table 10  |

| Truncated Filter Response Coefficients                               | 32     | Table 11  |

# TABLE OF CONTENTS

| 1. | Scope 1.1 References 1.1.1 Industry Documents 1.1.2 SFF Specifications 1.1.3 Sources 1.1.4 Conventions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 7<br>7<br>7<br>7<br>7                                                            |

|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|

| 2. | Power Requirements 2.1.1 Module Power Supply Requirements 2.1.2 Host Power Supply Noise Output 2.1.3 Module Power Supply Noise Output 2.1.4 Power Supply Noise Tolerance 2.2 ESD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8<br>8<br>8<br>8<br>10                                                           |

| 3. | Low Speed Interface 3.1 Introduction 3.2 Host Connector Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11<br>11<br>11                                                                   |

| 4. | Low Speed Electrical Control Contacts and 2-Wire Interface 4.1.1 Tx_Fault 4.1.2 Tx_Disable 4.1.3 RSO/RS1 4.1.4 Mod_ABS 4.1.5 SCL/SDA 4.1.6 Rx_LOS 4.2 Rate Select Hardware Control 4.3 Low Speed Electrical Specifications 4.3.1 Module Low Speed Electrical Specifications 4.3.2 Host Low speed Electrical Specifications 4.4. Timing Requirement of Control and Status I/O 4.4.1 Module Power On Initialization Procedure, Tx_Disable Negated 4.4.2 Module Power On Initialization Procedure, Tx_Disable Asserted. 4.4.3 Initialization During Hot Plugging 4.4.4 Transmitter Management 4.4.5 Transmitter Safety Detection and Presentation 4.4.6 Module Fault Recovery 4.4.7 Module Loss of Signal Indication | 14<br>14<br>14<br>14<br>14<br>15<br>15<br>16<br>16<br>17<br>18<br>19<br>20<br>20 |

| 5. | SFP+ 2-Wire Interface 5.1 Introduction 5.2 2-Wire Interface Electrical Specifications 5.3 SFP+ 2-Wire Timing Diagram 5.4 Memory Transaction Timing 5.5 Device Addressing and Operation 5.6 Read/Write Functionality 5.6.1 Memory Address Counter (Read and Write Operations) 5.6.2 Read Operations (Current Address Read) 5.6.3 Read Operations (Random Read) 5.6.4 Read Operations (Sequential Read) 5.6.5 Write Operations (Byte Write) 5.6.6 Write Operations (Sequential Write) 5.6.7 Write Operations (Acknowledge Polling)                                                                                                                                                                                  | 23<br>23<br>24<br>25<br>27<br>27<br>27<br>27<br>27<br>28<br>28<br>29             |

| Α. | Test Methodology And Measurement (Normative) A.1 Power Supply Testing Methodology A.1.1 Host Power Supply Noise Output A.1.2 SFP+ Module Power Supply Noise Output A.1.3 Module Power Supply Tolerance Testing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 30<br>30<br>30<br>31<br>32                                                       |

| _  | _  |    | -  |    |

|----|----|----|----|----|

|    | •  | ш  | IR | EC |

| г. | т, | JL | JΚ | EJ |

| Figure 1 Instantaneous and Sustained Peak Current for VccI or VccR            | 10 |

|-------------------------------------------------------------------------------|----|

| Figure 2 Host PCB SFP+ pad assignment top view                                | 11 |

| Figure 3 SFP+ Module Contact Assignment                                       | 12 |

| Figure 4 Power On Initialization of Module, Tx_Disable Negated                | 18 |

| Figure 5 Power On Initialization of Module, Tx_Disable Asserted               | 18 |

| Figure 6 Example of Initialization During Hot Plugging, Tx_Disable Negated    | 19 |

| Figure 7 Management of Module During Normal Operation, Tx_Disable Implemented | 19 |

| Figure 8 Occurrence of Condition Generating Tx_Fault                          | 20 |

| Figure 9 Successful Recovery from Transient Safety Fault Condition            | 21 |

| Figure 10 Unsuccessful Recovery from Safety Fault Condition                   | 21 |

| Figure 11 Timing of Rx_LOS Detection                                          | 22 |

| Figure 12 2-Wire Timing Diagram                                               | 24 |

| Figure 13 Detail of Clock Stretching                                          | 24 |

| Figure 14 Current Address Read Operation                                      | 27 |

| Figure 15 Random Read                                                         | 28 |

| Figure 16 Sequential Address Read Starting at Current Word Address            | 28 |

| Figure 17 Sequential Address Read Starting with Random Read                   | 28 |

| Figure 18 SFP+ Write Byte Operation                                           | 29 |

| Figure 19 Sequential Write Operation                                          | 29 |

| Figure 20 Module Compliance Board Power Supply Filters                        | 30 |

| Figure 21 Reference Filter Response                                           | 31 |

| Figure 22 Power Supply Noise Tolerance Test Setup                             | 32 |

|                                                                               |    |

| TABLES                                                                        | _  |

| Table 1 SFP+ Module Power Supply Requirements                                 | 9  |

| Table 2 SFP+ Module and Host Electrical contact definition                    | 13 |

| Table 3 Rate Select Hardware Control Contacts                                 | 15 |

| Table 4 Low Speed Module Electrical Specifications                            | 16 |

| Table 5 Low Speed Host Electrical Specifications                              | 16 |

| Table 6 Timing Parameters for SFP+ Management                                 | 16 |

| Table 7 2-Wire Interface Electrical Specifications                            | 23 |

| Table 8 SFP+ 2-Wire Timing Specifications                                     | 25 |

| Table 9 SFP+ Memory Specifications                                            | 25 |

| Table 10 SFP+ Device Address Word                                             | 27 |

| Table 11 Truncated Filter Response Coefficients                               | 31 |

SFF Committee --

# SFP+ Power and Low Speed Interface

### 1. Scope

This specification defines the low speed electrical and management interface specifications for SFP+ (enhanced Small Formfactor Pluggable) modules and hosts. The SFP+ module could be an electrical-to-optical or an electrical-to-electrical device.

#### 1.1 References

## 1.1.1 Industry Documents

The following interface standards are relevant to many SFF Specifications.

| INF-8074i | SFP (Small Formfactor Pluggable) 1 Gb/s Transceiver    |

|-----------|--------------------------------------------------------|

| INF-8077i | XFP 10 Gb/s 1X Pluggable Module                        |

| SFF-8071  | SFP+ 1X 0.8mm Card Edge Connector                      |

| SFF-8083  | SFP+ 1X 10 Gb/s Pluggable Transceiver Solution (SFP10) |

| SFF-8079  | SFP Rate and Application Selection                     |

| SFF-8089  | SFP Rate and Application Codes                         |

| SFF-8418  | SFP+ 10 Gb/s Electrical Interface                      |

| SFF-8431  | SFP+ 10 Gb/s and Low Speed Electrical Interface        |

| SFF-8432  | SFP+ 10 Gb/s Module and Cage                           |

| SFF-8472  | Management Interface for SFP+                          |

# 1.1.2 SFF Specifications

There are several projects active within the SFF Committee. The complete list of specifications which have been completed or are still being worked on are listed in the specification at <a href="ftp://ftp.seagate.com/sff/SFF-8000.TXT">ftp://ftp.seagate.com/sff/SFF-8000.TXT</a>

#### 1.1.3 Sources

Those who join the SFF Committee as an Observer or Member receive electronic copies of the minutes and SFF specifications (http://www.sffcommittee.com/ie/join.html).

Copies of ANSI standards may be purchased from the InterNational Committee for Information Technology Standards (http://www.techstreet.com/incitsgate.tmpl).

### 1.1.4 Conventions

The dimensioning conventions are described in ANSI-Y14.5M, Geometric Dimensioning and Tolerancing. All dimensions are in millimeters, which are the controlling dimensional units (if inches are supplied, they are for guidance only).

The ISO convention of numbering is used i.e., the thousands and higher multiples are separated by a space and a period is used as the decimal point. This is equivalent to the English/American convention of a comma and a period.

| American    | French      | ISO         |

|-------------|-------------|-------------|

| 0.6         | 0,6         | 0.6         |

| 1,000       | 1 000       | 1 000       |

| 1,323,462.9 | 1 323 462,9 | 1 323 462.9 |

### 2. Power Requirements

The module host has two 3.3 V power contacts, one supplying the module transmitter voltage (VccT) and the other supplying the module receiver voltage (VccR). The maximum current capacity, both continuous and peak, for each connector contact is 500 mA.

SFP+ module maximum power consumption shall meet one of the following power classes:

```

Power Level I modules - Up to 1.0 W

Power Level II modules - Up to 1.5 W

Power Level III modules - Up to 2.0 W

```

To avoid exceeding system power supply limits and cooling capacity, all modules at power up by default shall operate with up to 1.0 W. Hosts supporting Power Level II or III operation may enable a Power Level II or III module through the 2-wire interface. Power Level II or III modules shall assert the power level declaration bit of SFF-8472.

The maximum power level is allowed to exceed the classified power level for 500 ms following hot insertion or power up, or Power Level II or III authorization, however the current is limited to values given by Table 1 and illustrated in Figure 1.

At host power up the host shall supply VccT and VccR to the module within 100 ms of each other.

# 2.1.1 Module Power Supply Requirements

SFP+ module operates from the host supplied VccT and VccR. To protect the host and system operation, each SFP+ module during hot plug and normal operation shall follow the requirements listed in Table 1 and illustrated by Figure 1. The requirements for current apply to the current through each inductor of Figure 20 while the power supply voltages are defined at the SFP+ connector.

### 2.1.2 Host Power Supply Noise Output

The host shall generate an effective weighted integrated spectrum RMS noise less than 25 mV in the frequency range 10 Hz to 10 MHz, according to the methods of A.1.1.

# 2.1.3 Module Power Supply Noise Output

The module shall generate less than 15 mV RMS noise at point X of Figure 20 in the frequency range 10Hz to 10MHz, according to the methods of A.1.2.

# 2.1.4 Power Supply Noise Tolerance

SFP+ modules shall meet all electrical requirements and remain fully operational in the presence of a sinusoidal tolerance signal of amplitude given by Table 1 swept from 10 Hz to 10 MHz according to the methods of A.1.3. This emulates the worst case noise of the host.

It is also desirable for a module and host to each tolerate a degree of random or semi-random noise on both VccT and VccR simultaneously, but the characteristics of this noise are beyond the scope of this document.

#### TABLE 1 SFP+ MODULE POWER SUPPLY REQUIREMENTS

| TABLE I SITT MODULE TOWER S                                           | •··· = · · · · · · · · · · · · | <del>(</del> |      |      |      |  |  |  |

|-----------------------------------------------------------------------|--------------------------------|--------------|------|------|------|--|--|--|

| Parameters                                                            | Symbol                         | Condition    | Min  | Max  | Unit |  |  |  |

| Common Parameters                                                     |                                |              |      |      |      |  |  |  |

| Power supply noise tolerance including ripple [peak-to-peak]          |                                | see A.1.3    |      | 66   | mV   |  |  |  |

| Power supply voltages including ripple, droop and noise below 100 kHz | VccT,<br>VccR                  | *1           | 3.14 | 3.46 | V    |  |  |  |

| Instantaneous peak current at hot plug                                |                                | *2 *3        |      | 400  | mA   |  |  |  |

| Sustained peak current at hot plug                                    |                                | *2 *3 *5     |      | 330  | mA   |  |  |  |

| Power Level I M                                                       | lodu1e                         |              |      |      |      |  |  |  |

| Module maximum power consumption                                      |                                |              |      | 1.0  | W    |  |  |  |

| Power Level II                                                        | Module                         |              |      |      |      |  |  |  |

| Instantaneous peak current on enabling Power Level II                 |                                | *2 *3 *5     |      | 600  | mA   |  |  |  |

| Module sustained peak current on enabling Power Level II              |                                | *2 *3 *5     |      | 500  | mA   |  |  |  |

| Maximum power consumption at power up                                 |                                | *4           |      | 1.0  | W    |  |  |  |

| Module maximum power consumption                                      |                                |              |      | 1.5  | W    |  |  |  |

| Power Level III Module                                                |                                |              |      |      |      |  |  |  |

| Instantaneous peak current on enabling Power Level III                |                                | *2 *3 *5     |      | 800  | mA   |  |  |  |

| Module sustained peak current on enabling Power Level III             |                                | *2 *3 *5     |      | 660  | mA   |  |  |  |

| Maximum power consumption at power up                                 |                                | *4           |      | 1.0  | W    |  |  |  |

| Module maximum power consumption                                      |                                |              |      | 2.0  | W    |  |  |  |

- \*1 Set point is measured at the input to the connector on the host board reference to Vee. Droop is any temporary drop in voltage of the power supply such as that caused by plugging in another module or when enabling another module to Power Level II.

- \*2 The requirements for current apply to the current through each inductor of Figure 20.

- \*3 The maximum currents are the allowed currents for each power supply VccT or VccR, therefore the total module peak currents can be twice this value. The instantaneous peak current is allowed to exceed the specified maximum current capacity of the connector contact for a short period, see Figure 1.

- \*4 Maximum module power consumption shall not exceed 1.0 W from 500ms after power up until level II operation is enabled.

- \*5 Not to exceed the sustained peak limit for more than 50 us; may exceed this limit for shorter durations.

FIGURE 1 INSTANTANEOUS AND SUSTAINED PEAK CURRENT FOR VCCT OR VCCR

### 2.2 ESD

The SFP+ module and host SFI contacts (High Speed Contacts) shall withstand 1000 V electrostatic discharge based on Human Body Model per JEDEC JESD22-A114-B. The SFP+ module and all host contacts with exception of the SFI contacts (High Speed Contacts) shall withstand 2 kV electrostatic discharge based on Human Body Model per JEDEC JESD22-A114-B.

The SFP+ module shall meet ESD requirements given in EN61000-4-2, criterion B test specification such that units are subjected to 15 kV air discharges during operation and 8 kV direct contact discharges to the case.

# 3. Low Speed Interface

#### 3.1 Introduction

This specification has several enhancements over the classic SFP interface (INF-8074i), but the SFP+ host can be designed to also support most legacy SFP modules. SFP+ 2-wire interface electrical and timing specifications are defined in Section 5, and the SFP+ 2-wire interface management and register map are defined by SFF-8472.

### 3.2 Host Connector Definition

The SFP+ host connector is a 0.8 mm pitch 20 position improved connector specified by SFF-8071, or stacked connector with equivalent electrical performance. Host PCB contact assignment is shown in Figure 2 and contact definitions are given in Table 2. SFP+ module contacts mate with the host in the order of ground, power, followed by signal as illustrated by Figure 3 and the contact sequence order listed in Table 2.

FIGURE 2 HOST PCB SFP+ PAD ASSIGNMENT TOP VIEW

FIGURE 3 SFP+ MODULE CONTACT ASSIGNMENT

### TABLE 2 SFP+ MODULE AND HOST ELECTRICAL CONTACT DEFINITION

| Cont | Logic 1<br>*1 | Symbol     | Power<br>Sequence<br>Order | Name/Description                                                                                                  |    |

|------|---------------|------------|----------------------------|-------------------------------------------------------------------------------------------------------------------|----|

| case |               | case       | *2                         | Module case                                                                                                       |    |

| 1    |               | VeeT       | 1st                        | Module Transmitter Ground                                                                                         | *3 |

| 2    | LVTTL-0       | Tx_Fault   | 3rd                        | Module Transmitter Fault                                                                                          | *4 |

| 3    | LVTTL-I       | Tx_Disable | 3rd                        | Transmitter Disable; Turns off transmitter laser output                                                           | *5 |

| 4    | LVTTL-I/O     | SDA        | 3rd                        | 2-wire Serial Interface Data Line<br>(Same as MOD-DEF2 in INF-8074i)                                              | *6 |

| 5    | LVTTL-I/O     | SCL        | 3rd                        | 2-wire Serial Interface Clock (Same as MOD-DEF1 in INF-8074i)                                                     | *6 |

| 6    |               | Mod_ABS    | 3rd                        | Module Absent, connected to VeeT or VeeR in the module                                                            | *7 |

| 7    | LVTTL-I       | RS0        | 3rd                        | Rate Select O, optionally controls SFP+ module receiver.                                                          | *8 |

| 8    | LVTTL-0       | Rx_LOS     | 3rd                        | Receiver Loss of Signal Indication<br>(In FC designated as Rx_LOS and in<br>Ethernet designated as Signal Detect) | *4 |

| 9    | LVTTL-I       | RS1        | 3rd                        | Rate Select 1, optionally controls SFP+ module transmitter                                                        | *8 |

| 10   |               | VeeR       | 1st                        | Module Receiver Ground                                                                                            | *3 |

| 11   |               | VeeR       | 1st                        | Module Receiver Ground                                                                                            | *3 |

| 12   | CML-0         | RD-        | 3rd                        | Receiver Inverted Data Output                                                                                     |    |

| 13   | CML-0         | RD+        | 3rd                        | Receiver Non-Inverted Data Output                                                                                 |    |

| 14   |               | VeeR       | 1st                        | Module Receiver Ground                                                                                            | *3 |

| 15   |               | VccR       | 2nd                        | Module Receiver 3.3 V Supply                                                                                      |    |

| 16   |               | VccT       | 2nd                        | Module Transmitter 3.3 V Supply                                                                                   |    |

| 17   |               | VeeT       | 1st                        | Module Transmitter Ground                                                                                         | *3 |

| 18   | CML-I         | TD+        | 3rd                        | Transmitter Non-Inverted Data Input                                                                               |    |

| 19   | CML-I         | TD-        | 3rd                        | Transmitter Inverted Data Input                                                                                   |    |

| 20   |               | VeeT       | 1st                        | Module Transmitter Ground                                                                                         | *3 |

<sup>\*1</sup> Labeling as inputs (I) and outputs (0) are from the perspective of the module \*2 The case makes electrical contact to the cage before any of the board edge contacts are made.

<sup>\*3</sup> The module signal ground contacts, VeeR and VeeT, should be isolated from the module case.

<sup>\*4</sup> This contact is an open collector/drain output contact and shall be pulled up on the host see 4.1.1 and 4.1.6. Pull ups can be connected to one of several power supplies, however the host board design shall ensure that no module contact has voltage exceeding module VccT/R + 0.5 V.

<sup>\*5</sup> Tx\_Disable is an input contact with a 4.7 kOhms to 10 kOhms pullup to VccT inside the module.

<sup>\*6</sup> See 5.2

<sup>\*7</sup> See 4.1.4

<sup>\*8</sup> For SFF-8431 rate select definition see 4.1.3 and 4.2. (If implementing SFF-8079 contacts 7 and 9 in SFF-8431 are used for ASO and AS1 respectively).

### 4. Low Speed Electrical Control Contacts and 2-Wire Interface

In addition to the 2-wire serial interface, the SFP+ module has the following low speed contacts for control and status:

Tx\_Fault Tx\_Disable RSO/RS1 Mod\_ABS Rx\_LOS

#### 4.1.1 Tx\_Fault

Tx\_Fault is a module output that when high, indicates that the module transmitter has detected a fault condition related to laser operation or safety. If Tx\_Fault is not implemented, the Tx\_Fault contact signal shall be held low by the module and may be connected to Vee within the module.

The Tx\_Fault output is an open drain/collector and shall be pulled up to the Vcc\_Host in the host with a resistor in the range 4.7 kOhms to 10 kOhms, or with an active termination according to Table 5.

### 4.1.2 Tx\_Disable

When Tx\_Disable is asserted high or left open, the SFP+ module transmitter output shall be turned off unless the module is a passive cable assembly (see Appendix E in SFF-8418) in which case this signal may be ignored. This contact shall be pulled up to VccT with a 4.7 kOhms to 10 kOhms resistor in modules and cable assemblies. Tx\_Disable is a module input contact.

When Tx\_Disable is asserted low or grounded the module transmitter is operating normally.

### 4.1.3 RSO/RS1

RSO and RS1 are module inputs and are pulled low to VeeT with >30 kOhms resistors in the module. RSO optionally selects the optical receive signaling rate coverage. RS1 optionally selects the optical transmit signaling rate coverage. For logical definitions of RSO/RS1 see Section 4.2.

These contacts can also be used for ASO and AS1 if implementing SFF-8079. See SFF-8079 for details.

RS1 is commonly connected to VeeT or VeeR in the classic SFP modules. The host needs to ensure that it will not be damaged if this contact is connected to VeeT or VeeR in the module.

### 4.1.4 Mod ABS

Mod\_ABS is connected to VeeT or VeeR in the SFP+ module. The host may pull this contact up to Vcc\_Host with a resistor in the range 4.7 kOhms to 10 kOhms. Mod\_ABS is asserted 'High' when the SFP+ module is physically absent from a host slot. In the SFP MSA (INF-8074i) this contact has the same function but is called MOD\_DEFO.

#### 4.1.5 SCL/SDA

SCL is the 2-wire interface clock and SDA is the 2-wire interface data line. SCL and SDA are pulled up to Vcc\_Host\_2w by resistors in the host. For full specifications see Section 5.

#### 4.1.6 Rx LOS

Rx\_LOS when high indicates an optical signal level below that specified in the relevant standard. Rx\_LOS is an open drain/collector output, but may also be used

as an input by supervisory circuitry in the module. For a nominally 3.3 V Vcc\_Host using a resistive pull up to Vcc\_Host the resistor value shall be in the range 4.7 kOhms to 10 kOhms. For a nominally 2.5 V Vcc\_Host using a resistive pull up to Vcc\_Host the resistor value shall be in the range 4.7 kOhms to 7.2 kOhms. Alternatively, an active termination according to Table 5 may be used.

The Rx\_LOS signal is intended as a preliminary indication to the host in which the module is installed that the received signal strength is below the specified range. Such an indication typically points to non-installed cables, broken cables, or a disabled, failing or a powered off transmitter at the far end of the cable. Additional indications are provided by the host in which the module is installed to verify that the information being transmitted is valid, correctly encoded, and in the correct format. Such additional indications are outside the scope of the module specification.

Rx\_LOS may be an optional function depending on the supported standard. If the Rx\_LOS function is not implemented, or is reported via the two-wire interface only, the Rx\_LOS contact shall be held low by the module and may be connected to Vee within the module.

Rx\_LOS assert min and de-assert max are defined in the relevant standard. To avoid spurious transition of Rx\_LOS a minimum hysteresis of 0.5 dBo is recommended.

### 4.2 Rate Select Hardware Control

The SFP+ module provides two inputs RSO and RS1 that can optionally be used for rate selection. RSO controls the receive path signalling rate capability, and RS1 controls the transmit path signalling rate capability, as defined in Table 3. The host and module may choose to use either, both, or none of these functions. Because contact 9 in the classic SFP INF-8074i is connected to VeeR, an SFP+ host utilizing RS1 must provide short circuit protection.

This rate select functionality can also be controlled by software as defined by SFF-8472.

Optionally the rate select methods of Part 2 of SFF-8079 may be used instead of the method described here by setting the management declaration bit (A0h byte 93 bit 2) to 1, see SFF-8472.

| Parameter | State | Conditions                                        |  |  |  |  |  |  |  |  |

|-----------|-------|---------------------------------------------------|--|--|--|--|--|--|--|--|

| RS0       | Low   | RX signalling rate less than or equal to 4.25 GBd |  |  |  |  |  |  |  |  |

| KSU       | High  | RX signalling rate greater than 4.25 GBd          |  |  |  |  |  |  |  |  |

| RS1       | Low   | TX signalling rate less than or equal to 4.25 GBd |  |  |  |  |  |  |  |  |

| KST       | High  | TX signalling rate greater than 4.25 GBd          |  |  |  |  |  |  |  |  |

TABLE 3 RATE SELECT HARDWARE CONTROL CONTACTS

### 4.3 Low Speed Electrical Specifications

SFP+ low speed signalling is based on Low Voltage TTL (LVTTL) operating with a module supply of 3.3 V  $\pm$ 0.3 and with a host supply range of 2.38 to 3.46 V.

The 2-wire interface protocol and electrical specifications are defined in Section 5.

### 4.3.1 Module Low Speed Electrical Specifications

The SFP+ module low speed electrical specifications are given in Table 4. All I/O powered by VccT is referenced to VeeT and similarly VccR is referenced to VeeR.

TABLE 4 LOW SPEED MODULE ELECTRICAL SPECIFICATIONS

| Parameter    | Symbol Symbol | Min    | Max          | Unit | Conditions                                                                      |

|--------------|---------------|--------|--------------|------|---------------------------------------------------------------------------------|

| Module Vcc   | VccT, VccR    | 3.14   | 3.46         | V    |                                                                                 |

|              | VOL           | -0.3   | 0.40         | V    | At 0.7 mA *                                                                     |

| Tx_Fault,    | IOH 1         | -50    | 37.5         | uA   | Measured with a 4.7 kOhms load                                                  |

| Rx_LOS       |               |        |              |      | pulled up to Vcc_Host where                                                     |

|              |               |        |              |      | <pre>Vcc_Host_min<vcc_host<vcc_host_max< pre=""></vcc_host<vcc_host_max<></pre> |

| Tx_Disable   | VIL           | -0.3   | 0.80         | V    |                                                                                 |

| , RSO, RS1   | VIH           | 2.0    | VccT + 0.3   | V    |                                                                                 |

| * Positive v | alues indica  | te cur | rent flowing | into | the module.                                                                     |

# 4.3.2 Host Low speed Electrical Specifications

The SFP+ Host low speed electrical specifications are given in Table 5. All I/O powered by VccT is referenced to VeeT and similarly VccR is referenced to VeeR.

TABLE 5 LOW SPEED HOST ELECTRICAL SPECIFICATIONS

| Parameter  | Symbol   | Min  | Max    | Unit | Conditions                        |

|------------|----------|------|--------|------|-----------------------------------|

| Host Vcc   | Vcc_Host | 2.38 | 3.46   | V    |                                   |

| Pullup     |          |      |        |      |                                   |

| Tx_Fault,  | VIL      | *    | *      | V    |                                   |

| Rx_LOS     | VIH      | *    | *      | V    |                                   |

| Tx_Disable | VOL      | -0.3 | 0.4    | V    | VOL measured with 4.7 kOhms to 10 |

|            |          |      |        |      | kOhms pull up to VccT max         |

|            | VOH      | VccT | VccT + | V    | VOH measured with 10 kOhms pull   |

|            |          | -0.5 | 0.3    |      | up to VccT min                    |

|            | VOL      | -0.3 | 0.4    | V    | VOL measured with no load         |

| RSO, RS1   | VOH      | 2.2  | VccT + | V    | VOH measured with 30 kOhms to     |

|            |          |      | 0.3    |      | VeeR.                             |

<sup>\*</sup> Determined by host design, such that VIH > 2.1 V for the range of IOH in Table 4. One option is using standard LVTTL input with a pull-up to Vcc\_Host in the range 4.7 kOhms to 10 kOhms

# 4.4 Timing Requirement of Control and Status I/O

The timing requirements of control and status I/O are defined in Table 6, and are applicable to a power supply meeting the SFP+ Module Power Supply Requirements defined in SFF-8418.

TABLE 6 TIMING PARAMETERS FOR SFP+ MANAGEMENT

| Parameter                           | Symbol Symbol | Min | Max | Unit | Conditions                                                                                                                                              |

|-------------------------------------|---------------|-----|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Tx_Disable<br>assert<br>time        | t_off         |     | 100 | us   | Rising edge of Tx_Disable to fall of output signal below 10% of nominal                                                                                 |

| Tx_Disable negate time              | t_on          |     | 2   | ms   | Falling edge of Tx_Disable to rise of output signal above 90% of nominal. This only applies in normal operation, not during start up or fault recovery. |

| Time to initialize 2-wire interface | t_2w_start_up |     | 300 | ms   | From power on or hot plug.                                                                                                                              |

| Time to initialize                  | t_start_up    |     | 300 | ms   | From power on or hot plug or Tx disable negated during power up,                                                                                        |

|                                                                                         | 1                  |    |     |    |                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------|--------------------|----|-----|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                         |                    |    |     |    | or Tx_Fault recovery, until non-cooled power level I part (or non-cooled power level II part already enabled at power level II for Tx_Fault recovery) is fully operational.                                                                                                                                        |

| Time to initialize cooled module and time to power up a cooled module to Power Level II | t_start_up_cooled  |    | 90  | S  | From power on or hot plug, or Tx disable negated during power up or Tx_Fault recovery, until cooled power level I part (or cooled power level II part during fault recovery) is fully operational. Also, from stop bit low-to-high SDA transition enabling Power Level II until cooled module is fully operational |

| Time to<br>Power Up<br>to Level<br>II                                                   | t_power_level2     |    | 300 | ms | From stop bit low-to-high SDA transition enabling power level II until non-cooled module is fully operational                                                                                                                                                                                                      |

| Time to<br>Power Down<br>from Level<br>II                                               | t_power_down       |    | 300 | ms | From stop bit low-to-high SDA transition disabling power level II until module is within power level I requirements                                                                                                                                                                                                |

| Tx_Fault assert                                                                         | Tx_Fault_on        |    | 1   | ms | From occurrence of fault to assertion of Tx_Fault                                                                                                                                                                                                                                                                  |

| Tx_Fault assert for cooled module                                                       | Tx_Fault_on_cooled |    | 50  | ms | From occurrence of fault to assertion of Tx_Fault                                                                                                                                                                                                                                                                  |

| Tx_Fault<br>Reset                                                                       | t_reset            | 10 |     | us | Time Tx_Disable must be held high to reset Tx_Fault                                                                                                                                                                                                                                                                |

| RSO, RS1<br>rate<br>select<br>timing for<br>FC                                          | t_RSO_FC, t_RS1_FC |    | 500 | us | From assertion till stable output                                                                                                                                                                                                                                                                                  |

| RSO, RS1<br>rate<br>select<br>timing non<br>FC                                          | t_RSO, t_RS1       |    | 24  | ms | From assertion till stable output                                                                                                                                                                                                                                                                                  |

| Rx_LOS<br>assert<br>delay                                                               | t_los_on           |    | 100 | us | From occurrence of loss of signal to assertion of Rx_LOS                                                                                                                                                                                                                                                           |

| Rx_LOS<br>negate<br>delay                                                               | t_los_off          |    | 100 | us | From occurrence of presence of signal to negation of Rx_LOS                                                                                                                                                                                                                                                        |

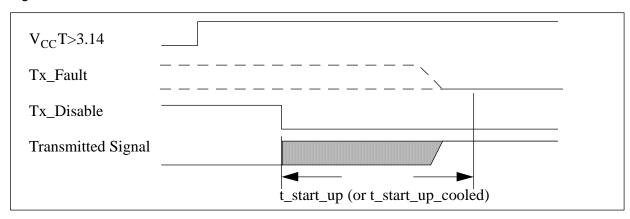

### 4.4.1 Module Power On Initialization Procedure, Tx\_Disable Negated

During power on of the module, Tx\_Fault, if implemented, may be asserted (high) as soon as power supply voltages are within specification. For module initialization with Tx\_Disable negated, Tx\_Fault shall be negated when the transmitter safety circuitry, if implemented, has detected that the transmitter is operating in its normal state. If a transmitter fault has not occurred, Tx\_Fault shall be negated within a period t\_start\_up from the time that VccT exceeds the specified minimum operating voltage (see SFF-8418 SFP+ Module Power Supply Requirements). If the

Tx\_Fault remains asserted after t\_start\_up, the host shall determine whether the module is cooled by reading the status bit over 2-wire interface. If the module is not cooled, the host may assume that a transmission fault has occurred. If the module is cooled, the host may assume that a transmission fault has occurred if Tx\_Fault remains asserted beyond t\_start\_up\_cooled.

The power on initialization timing for a module with Tx\_Disable negated is shown in Figure 4.

FIGURE 4 POWER ON INITIALIZATION OF MODULE, TX\_DISABLE NEGATED

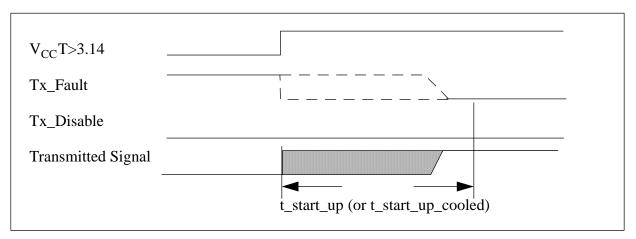

## 4.4.2 Module Power On Initialization Procedure, Tx\_Disable Asserted.

For module power on initialization with Tx\_Disable asserted, the state of Tx\_Fault is not defined while Tx\_Disable is asserted. After Tx\_Disable is negated, Tx\_Fault may be asserted while safety circuit initialization is performed. Tx\_Fault shall be negated when the transmitter safety circuitry, if implemented, has detected that the transmitter is operating in its normal state. If a transmitter fault has not occurred, Tx\_Fault shall be negated within a period t\_start\_up from the time that Tx\_Disable is negated. If Tx\_Fault remains asserted beyond the period t\_start\_up, the host may assume that a transmission fault has been detected by the module.

If no transmitter safety circuitry is implemented, the  $Tx_Fault$  signal may be tied to its negated state.

The power on initialization timing for a module with Tx\_Disable asserted is shown in Figure 5.

FIGURE 5 POWER ON INITIALIZATION OF MODULE, TX\_DISABLE ASSERTED

### 4.4.3 Initialization During Hot Plugging

When a module is not installed, Tx\_Fault is held to the asserted state by the pull up circuits on the host. As the module is installed, contact is made with the ground, voltage, and signal contacts in the specified order. After the module has determined that VccT has reached the specified value, the power on initialization takes place as described in the previous section. An example of initialization during hot plugging is provided in Figure 6.

FIGURE 6 EXAMPLE OF INITIALIZATION DURING HOT PLUGGING, TX\_DISABLE NEGATED

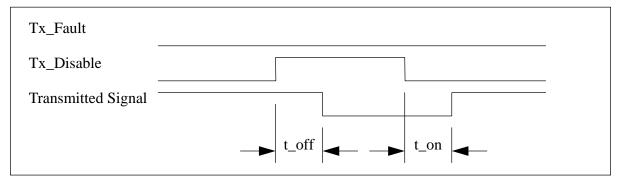

# 4.4.4 Transmitter Management

The timing requirements for the management of optical outputs from the module using the Tx\_Disable signal are shown in Figure 7. Note that t\_on time refers to the maximum delay until the modulated optical signal reaches 90% of the final value, not just the average optical power.

FIGURE 7 MANAGEMENT OF MODULE DURING NORMAL OPERATION, TX\_DISABLE IMPLEMENTED

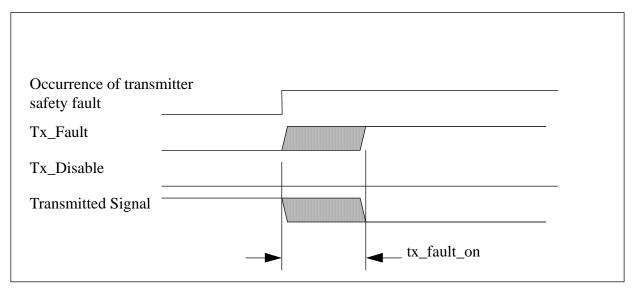

### 4.4.5 Transmitter Safety Detection and Presentation

If Tx\_Fault is implemented it shall meet the timing requirements of Figure 8.

FIGURE 8 OCCURRENCE OF CONDITION GENERATING TX\_FAULT

### 4.4.6 Module Fault Recovery

The detection of a safety-related transmitter fault condition presented by Tx\_Fault shall be latched. The following protocol may be used to reset the latch in case the transmitter fault condition is transient.

To reset the fault condition and associated detection circuitry, Tx\_Disable shall be asserted for a minimum of t\_reset. Tx\_Disable shall then be negated. Alternatively the Software Tx disable is asserted and negated. In less than the maximum value of t\_start\_up the optical transmitter will correctly reinitialize the laser circuits, negate Tx\_Fault, and begin normal operation if the fault condition is no longer present.

If a fault condition is detected during the reinitialization, Tx\_Fault shall again be asserted, the fault condition again latched, and the optical transmitter circuitry will again be disabled until the next time a reset protocol is attempted. The manufacturer of the module shall ensure that the optical power emitted from an open connector or fiber is compliant with applicable eye safety requirements during all reset attempts, during normal operation or upon the occurrence of reasonable single fault conditions.

The module may require internal protective circuitry to prevent the frequent assertion of the Tx\_Disable signal from generating frequent pulses of energy that violate the safety requirements. Timing for successful recovery from a transient safety fault condition is shown in Figure 9.

FIGURE 9 SUCCESSFUL RECOVERY FROM TRANSIENT SAFETY FAULT CONDITION

An example of an unsuccessful recovery, where the fault condition was not transient is shown in Figure 10.

FIGURE 10 UNSUCCESSFUL RECOVERY FROM SAFETY FAULT CONDITION

# 4.4.7 Module Loss of Signal Indication

If the module is specified as implementing Rx\_LOS, the timing is specified in Figure 11.

FIGURE 11 TIMING OF RX\_LOS DETECTION

### 5. SFP+ 2-Wire Interface

### 5.1 Introduction

The SFP+ management interface is a two-wire interface, similar to I2C. SFP+ management memory map is specified by SFF-8472. Nomenclature for all registers more than 1 bit long are MSB...LSB (MSB transmitted first).

## 5.2 2-Wire Interface Electrical Specifications

The SFP+ 2-wire interface specifications are given in Table 7. These specifications ensure compatibility between host masters and SFP+ SCL/SDA lines and compatibility with I2C. All voltages are referenced to VeeT.

TABLE 7 2-WIRE INTERFACE ELECTRICAL SPECIFICATIONS

| Parameter                                 | Symbol      | Max                  | Max                  | Unit | Conditions                                                                |

|-------------------------------------------|-------------|----------------------|----------------------|------|---------------------------------------------------------------------------|

| Host 2-wire Vcc                           | Vcc_Host_2w | 3.14                 | 3.46                 | V    | *1                                                                        |

| SCL and SDA                               | VOL         | 0.0                  | 0.40                 | V    | <pre>Rp2w 2 pulled toVcc_Host_2w, *3</pre>                                |

| SCL and SDA                               | VOH         | Vcc_Host_2w<br>- 0.5 | Vcc_Host_2w<br>+ 0.3 | V    | <pre>Rp2w 2 pulled to Vcc_Host_2w, *3</pre>                               |

| SCL and SDA                               | VIL         | -0.3                 | VccT * 0.3           | V    | *3                                                                        |

| SCL alla SDA                              | VIH         | VccT * 0.7           | VccT + 0.5           | V    | *3                                                                        |

| Input current on the SCL and SDA contacts | 11          | -10                  | 10                   | uA   |                                                                           |

| Capacitance on SCL and SDA I/O contact    | Ci 4        |                      | 14                   | pF   |                                                                           |

| Total bus capacitance for                 |             |                      | 100                  | pF   | At 400 kHz, 3.0<br>kOhms Rp2w, max<br>At 100 kHz, 8.0<br>kOhms Rp2w, max  |

| SCL and for SDA                           | Cb 5        |                      | 290                  | pF   | At 400 kHz, 1.1<br>kOhms Rp2w, max<br>At 100 kHz, 2.75<br>kOhms Rp2w, max |

<sup>\*1</sup> The Host 2-wire Vcc is the voltage used for resistive pull ups for the 2 wire interface

$<sup>^*2</sup>$  Rp2w is the pull up resistor. Active bus termination may be used by the host in place of a pullup resistor. Pull ups can be connected to any one of several power supplies, however the host board design shall ensure that no module contact has voltage exceeding module VccT/R + 0.5 V nor requires the module to sink more than 3.0 mA current.

<sup>\*3</sup> These voltages are measured on the other side of the connector to the device under test.

<sup>\*4</sup> Ci is the capacitance looking into the module SCL and SDA contacts

<sup>\*5</sup> Cb is the total bus capacitance on the SCL or SDA bus.

# 5.3 SFP+ 2-Wire Timing Diagram

SFP+ 2-wire bus timing is shown in Figure 12 and the detail of clock stretching is shown in Figure 13. SFP+ 2-wire timing specifications are given in Table 8.

FIGURE 12 2-WIRE TIMING DIAGRAM

FIGURE 13 DETAIL OF CLOCK STRETCHING

The 2-wire serial interface addresses of the SFP+ module are 1010000x (A0h) and 1010001x (A2h).

TABLE 8 SFP+ 2-WIRE TIMING SPECIFICATIONS

| Parameter                                       | Symbol Symbol | Max | Max  | Unit | Conditions                                                                                                                                                                  |

|-------------------------------------------------|---------------|-----|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Frequency                                 | fSCL          | 0   | 400  | kHz  | Module shall operate with fSCL up<br>to 100 kHz without requiring<br>clock stretching. The module may<br>clock stretch with fSCL greater<br>than 100 kHz and up to 400 kHz. |

| Clock Pulse Width Low                           | tLOW          | 1.3 |      | us   |                                                                                                                                                                             |

| Clock Pulse Width High                          | tHIGH         | 0.6 |      | us   |                                                                                                                                                                             |

| Time bus free before new transmission can start | tBUF          | 20  |      | us   | Between STOP and START and between ACK and ReSTART                                                                                                                          |

| START Hold Time                                 | tHD,STA       | 0.6 |      | us   |                                                                                                                                                                             |

| START Set-up Time                               | tSU,STA       | 0.6 |      | us   |                                                                                                                                                                             |

| Data In Hold Time                               | tHD,DAT       | 0   |      | us   |                                                                                                                                                                             |

| Data In Set-up Time                             | tSU,DAT       | 0.1 |      | us   |                                                                                                                                                                             |

| Input Rise Time (100 kHz)                       | tR,100        |     | 1000 | ns   | From (VIL,MAX - 0.15) to (VIH,MIN + 0.15)                                                                                                                                   |

| Input Rise Time (400 kHz)                       | tR,400        |     | 300  | ns   | From (VIL,MAX - 0.15) to (VIH,MIN + 0.15)                                                                                                                                   |

| Input Fall Time (100 kHz)                       | tF,100        |     | 300  | ns   | From (VIH,MIN + 0.15) to (VIL,MAX - 0.15)                                                                                                                                   |

| Input Fall Time (400 kHz)                       | tF,400        |     | 300  | ns   | From (VIH,MIN + 0.15) to (VIL,MAX - 0.15)                                                                                                                                   |

| STOP Set-up Time                                | tSU,STO       | 0.6 |      | us   |                                                                                                                                                                             |

# 5.4 Memory Transaction Timing

SFP+ memory transaction timings are given in Table 9.

TABLE 9 SFP+ MEMORY SPECIFICATIONS

| Parameter                                               | Symbo1           | Max | Max | Unit   | Conditions                                                                                              |

|---------------------------------------------------------|------------------|-----|-----|--------|---------------------------------------------------------------------------------------------------------|

| Serial Interface Clock<br>Holdoff 'Clock<br>Stretching' | T_clock<br>_hold |     | 500 | us     | Maximum time the SFP+ module may hold the SCL line low before continuing with a read or write operation |

| Complete Single or<br>Sequential Write up to<br>4 Byte  | tWR              |     | 40  | ms     |                                                                                                         |

| Complete Sequential<br>Write of 5-8 Byte                | tWR              |     | 80  | ms     |                                                                                                         |

| Endurance (Write Cycles)                                |                  | 10k |     | cycles |                                                                                                         |

# 5.5 Device Addressing and Operation

Serial Clock (SCL)

The host supplied SCL input to SFP+ transceivers is used to positively edge clock data into each SFP+ device and negative edge clock data out of each device. The SCL line may be pulled low by an SFP+ module during clock stretching.

Serial Data (SDA)

The SDA contact is bi-directional for serial data transfer. This contact is open-drain or open-collector driven and may be wire-ORed with other open-drain or open collector devices with different device addresses, provided the total bus capacitance

meets the requirement of Table 7 and the Serial Clock (SCL) is also wire-ORed.

Master/Slave

SFP+ transceivers operate only as slave devices. The host must provide a bus master for SCL and initiate all read/write communication

**Device Address**

communication.

Each SFP+ is hard wired at the device addresses A0h and A2h.

See SFF-8472 for memory structure within each transceiver.

The SDA contact is normally pulled high with an external

Clock and Data Transitions See SFF-8472 for memory structure within each transceiver. The SDA contact is normally pulled high with an external device. Data on the SDA contact may change only during SCL low time periods. Data changes during SCL high periods indicate a START or STOP condition. All addresses and data words are serially transmitted to and from the SFP+ in 8-bit words. Every byte on the SDA line must be 8-bits long. Data is transferred with the most significant bit (MSB) first.

**START Condition**

A high-to-low transition of SDA with SCL high is a START condition, which must precede any other command.

STOP Condition

A low-to-high transition of SDA with SCL high is a STOP condition.

Acknowledge

After sending each 8-bit word, the transmitter releases the SDA line for one bit time, during which the receiver is allowed to pull SDA low (zero) to acknowledge (ACK) that it has received each word. Device address bytes and write data bytes initiated by the host shall be acknowledged by SFP+ transceivers. Read data bytes transmitted by SFP+ transceivers shall be acknowledged by the host for all but the final byte read, for which the host shall respond with a STOP instead of an ACK. When a slave is unable to receive or transmit, because, e.g., it is performing a higher priority function, the data line shall be left high by the slave. A NACK is generated when the slave leaves the data line high during the ACK clock pulse. The master can then generate either a STOP condition to abort the transfer or a repeated START condition to start a new transfer.

Non-acknowledge (NACK)

When in a transfer, a master-receiver must signal the end of data to the slave-transmitter by not generating an acknowledge on the last byte clocked out of the slave. A NACK is generated when the master leaves the data line High during the ACK clock pulse. The slave-transmitter must release the data line to permit the master to generate a STOP or repeated START condition.

Memory (Management Interface) Reset After an interruption in protocol, power loss or system reset the SFP+ management interface can be reset. Memory reset is intended only to reset the SFP+ transceiver management interface (to correct a hung bus). No other transceiver functionality is implied.

- 1. Clock up to 9 cycles.

- 2. Look for SDA high in each cycle while SCL is high.

- 3. Create a START condition as SDA is high.

**Device Addressing**

SFP+ devices require an 8 bit device address word following a start condition to enable a read or write operation. The device addresses to select AOh or A2h are shown in Table 10. This is common to all SFP+ devices.

TABLE 10 SFP+ DEVICE ADDRESS WORD

| Address |     |   |   |   |   |   | Address<br>Select | R/W<br>select |

|---------|-----|---|---|---|---|---|-------------------|---------------|

| A0h     | 1   | 0 | 1 | 0 | 0 | 0 | 0                 | Х             |

| A2h     | 1   | 0 | 1 | 0 | 0 | 0 | 1                 | Х             |

|         | MSB |   |   |   |   |   |                   | LSB           |

The LSB of the device address word is the read/write operating select bit. A read operation is initiated if this bit is set high and a write operation is initiated if this bit is set low.

# 5.6 Read/Write Functionality

The methods for reading from and writing to the two different SFP+ addresses A0h and A2h are described in this section. They are identical for the two different addresses except that the appropriate address is used for each read and write. For simplicity in the figures the address is labelled 101000x where the x is 0 for the A0h address and 1 for the A2h address. Note that the address here is only seven bits. In order to complete the full 8 bit byte a one or zero is added to the end of the address depending on whether a read or a write operation is taking place.

### 5.6.1 Memory Address Counter (Read and Write Operations)

SFP+ devices maintain two internal data word address counters one for each address. These counters contain the last address accessed during the latest read or write operation, incremented by one. The address counter is incremented whenever a data word is received or sent by the transceiver. This address stays valid between operations as long as SFP+ power is maintained. The address 'roll over' during read and write operations is from the last byte of the 256 byte memory page to the first byte of the same page.

### 5.6.2 Read Operations (Current Address Read)

A current address read operation requires only that the device address read word (10100001 or 10100011) be sent, Figure 14. Once acknowledged by the SFP+, the current address data word is serially clocked out. The host does not respond with an acknowledge, but does generate a STOP condition once the data word is read.

|      |                       | < -         | - SF | P+ A | ADD | RES | S -> |             |                  |             |             |   |     |      |     |      |   |             |                  |                  |

|------|-----------------------|-------------|------|------|-----|-----|------|-------------|------------------|-------------|-------------|---|-----|------|-----|------|---|-------------|------------------|------------------|

| HOST | S<br>T<br>A<br>R<br>T | M<br>S<br>B |      |      |     |     |      | L<br>S<br>B | R<br>E<br>A<br>D |             |             |   |     |      |     |      |   |             | N<br>A<br>C<br>K | S<br>T<br>O<br>P |

|      |                       | 1           | 0    | 1    | 0   | 0   | 0    | х           | 1                | 0           | х           | х | х   | x    | x   | x    | x | x           | 1                |                  |

| SFP+ |                       |             |      |      |     |     |      |             |                  | A<br>C<br>K | M<br>S<br>B |   |     |      |     |      |   | L<br>S<br>B |                  |                  |

|      |                       |             |      |      |     |     |      |             |                  |             | <-          |   | DA' | TA V | WO! | RD - |   | >           |                  |                  |

FIGURE 14 CURRENT ADDRESS READ OPERATION

# 5.6.3 Read Operations (Random Read)

A random read operation requires a 'dummy' write operation to load in the target byte address Figure 15. This is accomplished by the following sequence: The target 8-bit data word address is sent following the device address write word (10100000 or 10100010) and acknowledged by the SFP+. The host then generates another START condition (aborting the dummy write without incrementing the counter) and a current address read by sending a device read address (10100001 or 10100011). The SFP+ acknowledges the device address and serially clocks out the requested data word.

The host does not respond with an acknowledge, but does generate a STOP condition once the data word is read.

|      |                       | < -         | - SF | P+ 4 | ADL | RES | SS -> | ,           |                       |             | <-          | ME | MO. | RY A | ADI | RE | SS -> | ,           |             |                       | < -         | - SF | P+ A | ADE | RES | SS | >           |                  |             |             |   |    |      |     |      |   |             |                  |                  |

|------|-----------------------|-------------|------|------|-----|-----|-------|-------------|-----------------------|-------------|-------------|----|-----|------|-----|----|-------|-------------|-------------|-----------------------|-------------|------|------|-----|-----|----|-------------|------------------|-------------|-------------|---|----|------|-----|------|---|-------------|------------------|------------------|

| HOST | S<br>T<br>A<br>R<br>T | M<br>S<br>B |      |      |     |     |       | L<br>S<br>B | W<br>R<br>I<br>T<br>E |             | M<br>S<br>B |    |     |      |     |    |       | L<br>S<br>B |             | S<br>T<br>A<br>R<br>T | M<br>S<br>B |      |      |     |     |    | L<br>S<br>B | R<br>E<br>A<br>D |             |             |   |    |      |     |      |   |             | N<br>A<br>C<br>K | S<br>T<br>O<br>P |

|      |                       | 1           | 0    | 1    | 0   | 0   | 0     | х           | 0                     | 0           | х           | х  | х   | х    | х   | х  | х     | х           | 0           |                       | 1           | 0    | 1    | 0   | 0   | 0  | х           | 1                | 0           | х           | х | х  | х    | х   | х    | х | х           | 1                |                  |

| SFP+ |                       |             |      |      |     |     |       |             |                       | A<br>C<br>K |             |    |     |      |     |    |       |             | A<br>C<br>K |                       |             |      |      |     |     |    |             |                  | A<br>C<br>K | M<br>S<br>B |   |    |      |     |      |   | L<br>S<br>B |                  |                  |

|      |                       |             |      |      |     |     |       |             |                       |             |             |    |     |      |     |    |       |             |             |                       |             |      |      |     |     |    |             |                  |             | <           | < | DA | TA Y | WOI | RD - | > |             |                  |                  |

FIGURE 15 RANDOM READ

# 5.6.4 Read Operations (Sequential Read)

Sequential reads are initiated by either a current word address read Figure 16 or a random address read Figure 17. To specify a sequential read, the host responds with an acknowledge (instead of a STOP) after each data word. As long as the SFP+ receives an acknowledge, it shall serially clock out sequential data words. The sequence is terminated when the host responds with a NACK and a STOP instead of an acknowledge.

|      |                       | < -         | - SF | P+ / | ADE | RE | SS -> | >           |                  |             |             |   |     |      |     |     |    |             |             |             |   |     |   |     |    |   |             |             |             |   |     |   |     |     |   |             |                  |                  |

|------|-----------------------|-------------|------|------|-----|----|-------|-------------|------------------|-------------|-------------|---|-----|------|-----|-----|----|-------------|-------------|-------------|---|-----|---|-----|----|---|-------------|-------------|-------------|---|-----|---|-----|-----|---|-------------|------------------|------------------|